# MAINTENANCE MANUAL

# PORTABLE HF-SSB/AM RADIO SET PRC-2200

JANUARY 1992

Page

# LIST OF ILLUSTRATIONS

| 19. M                     |            |               |

|---------------------------|------------|---------------|

| - 10 XO, 2010 - 1771 - 17 | <b>1 1</b> |               |

| 100.00 × 0.00 × 1         | .cie       | (2) X.1 CANAX |

|                           |            |               |

|                           | - / CA     |               |

|                           |            |               |

|                           |            |               |

|                           |            |               |

|                           |            |               |

|                           |            |               |

|                           |            |               |

|                           |            |               |

|                           |            |               |

|                           |            |               |

Figure

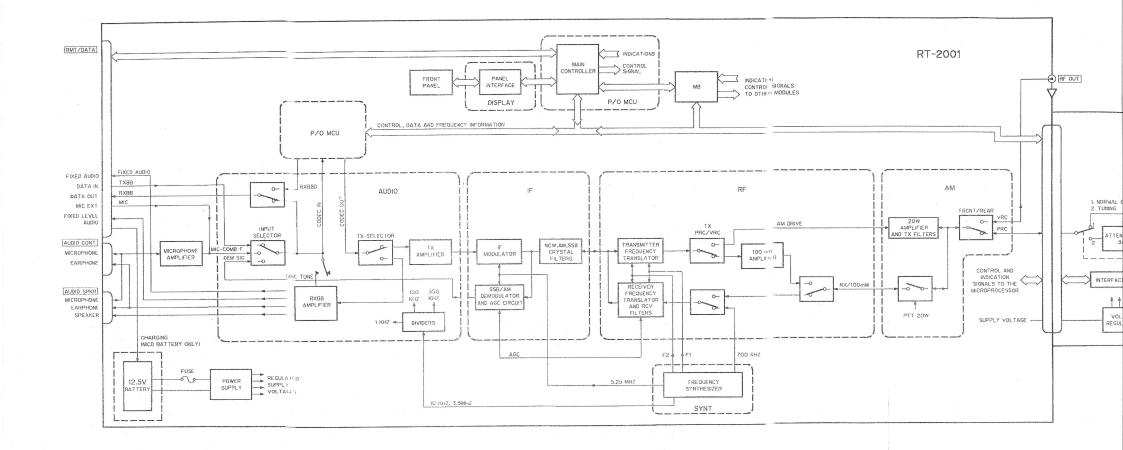

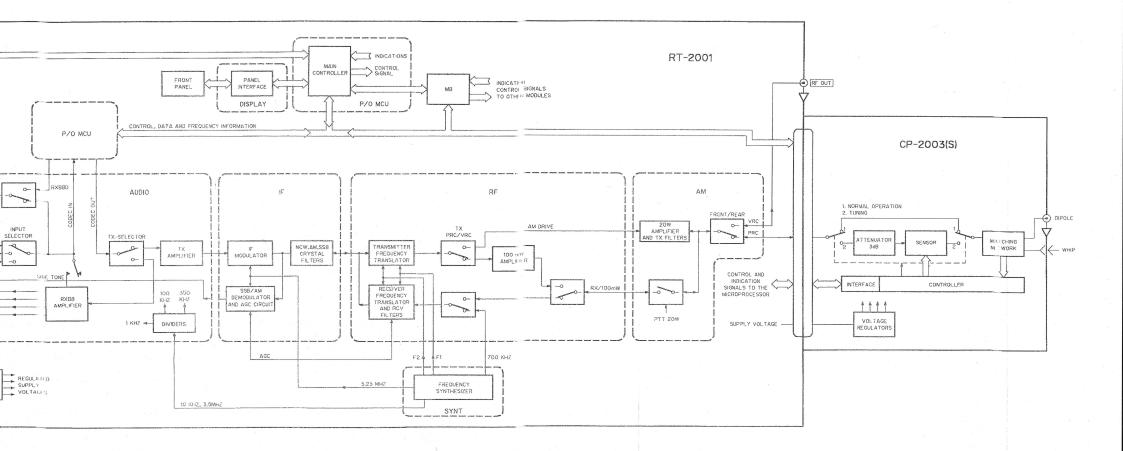

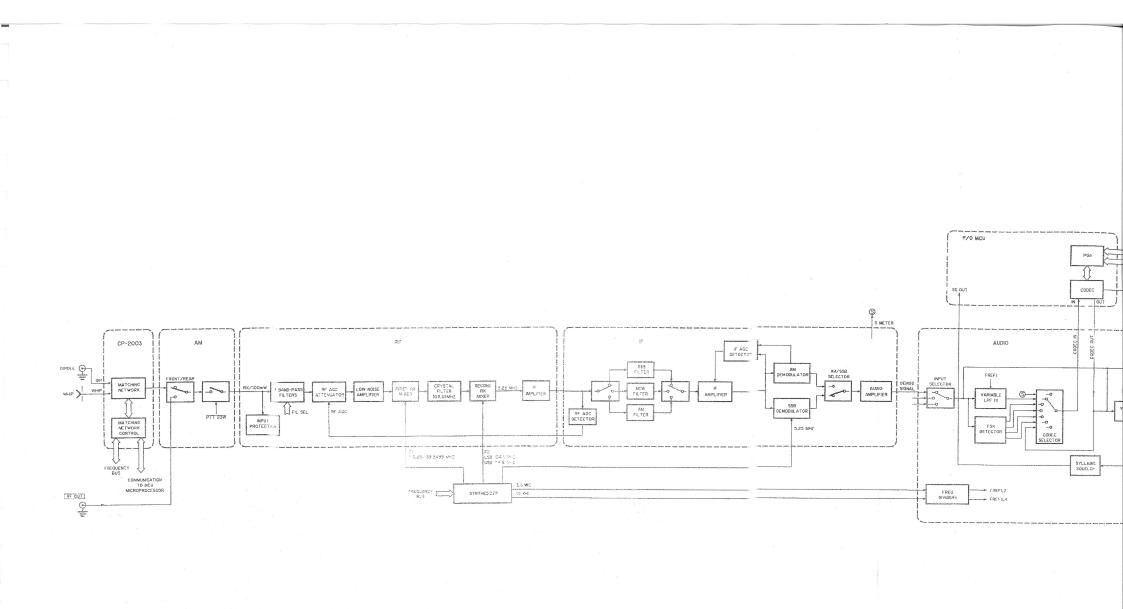

|               | 2-1                                                                                                                                                                                                                                | PRC-2200, Block Diagram                                      | 2-7   |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------|

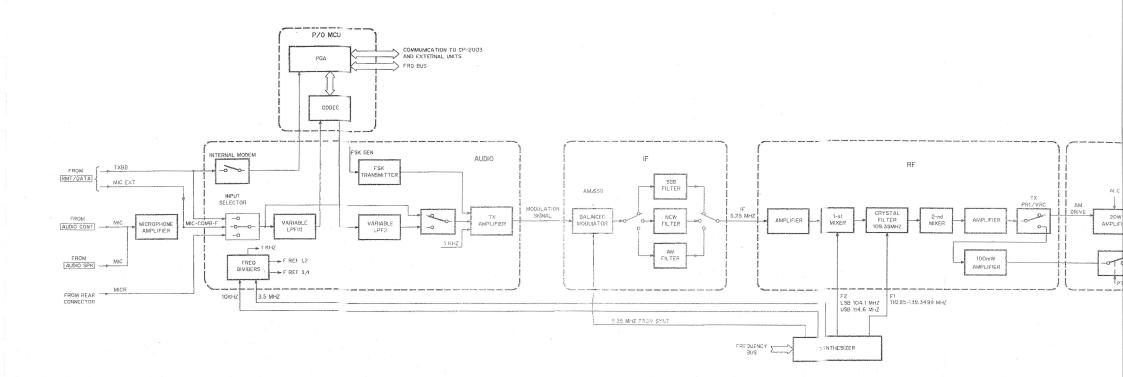

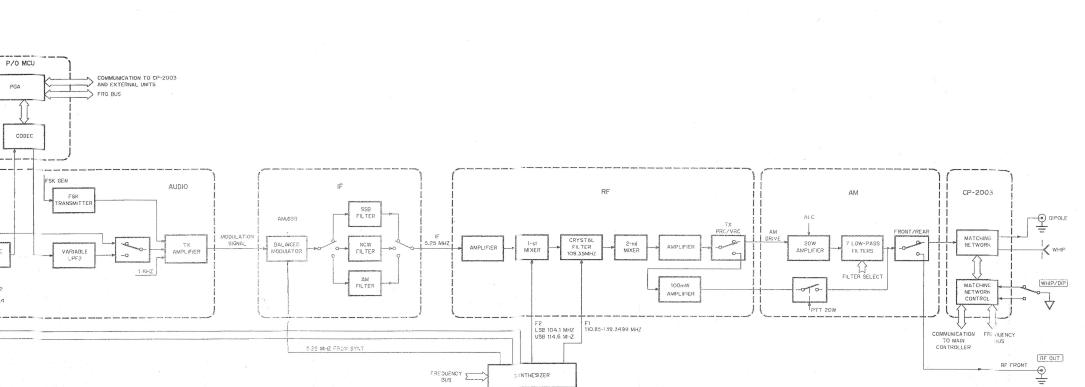

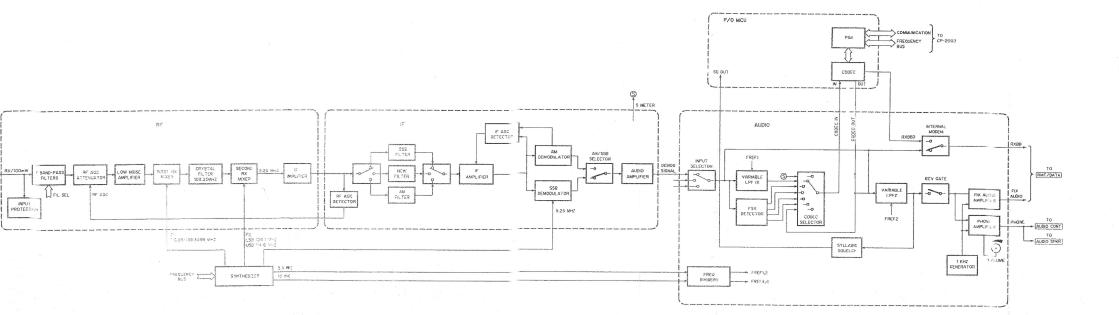

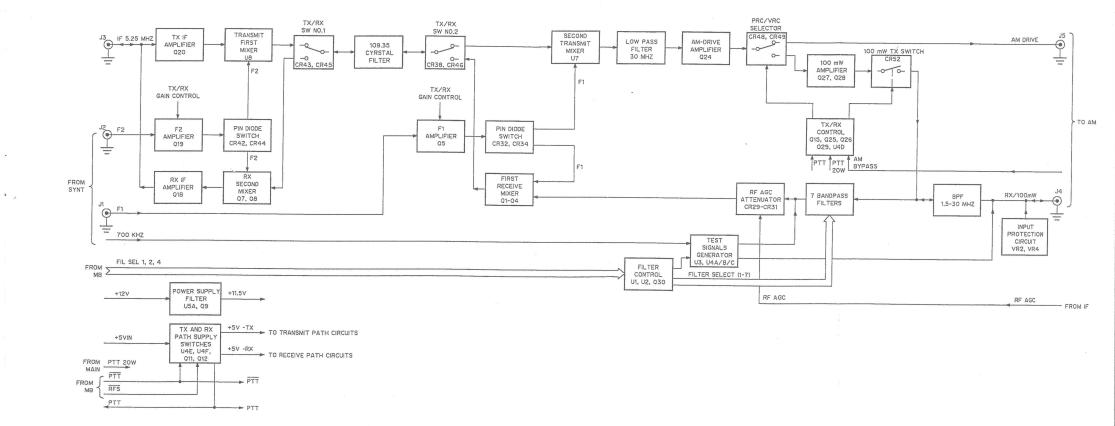

|               | 2-2                                                                                                                                                                                                                                | Transmit Path, Block Diagram                                 | 2-11  |

|               | 2-3                                                                                                                                                                                                                                | Receive Path, Block Diagram                                  | 2-15  |

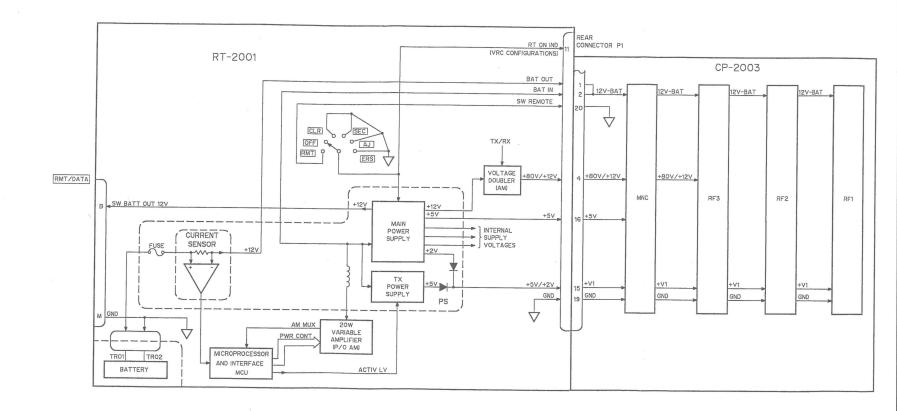

|               | 2-4                                                                                                                                                                                                                                | PRC-2200, Power Supply System                                | 2-19  |

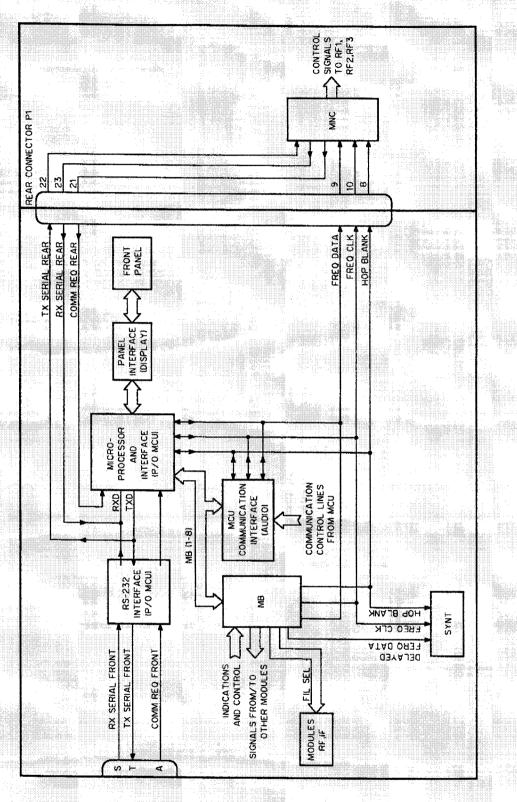

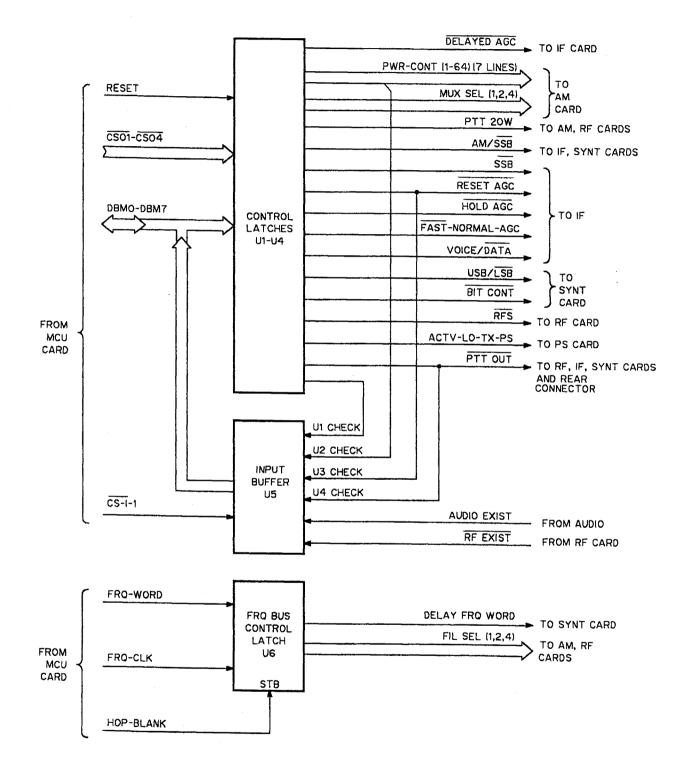

|               | 2-5                                                                                                                                                                                                                                | Control Sub-System of PRC-2200                               | 2-22  |

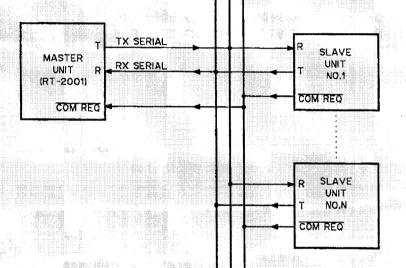

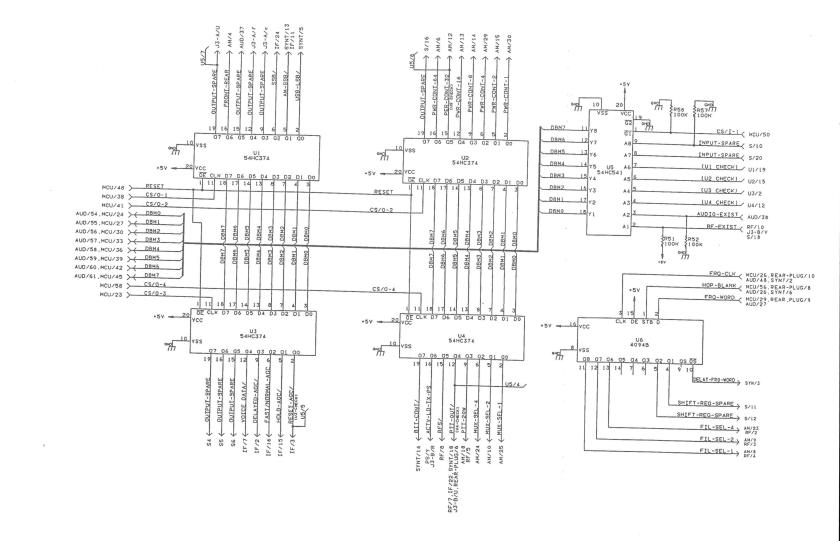

| <b>700000</b> | 2-6                                                                                                                                                                                                                                | Control Communication System Configuration                   | 2-24  |

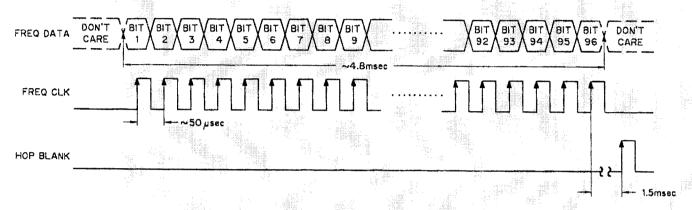

|               | 2-7                                                                                                                                                                                                                                | Serial Frequency Bus, Timing and Format                      | 2-27  |

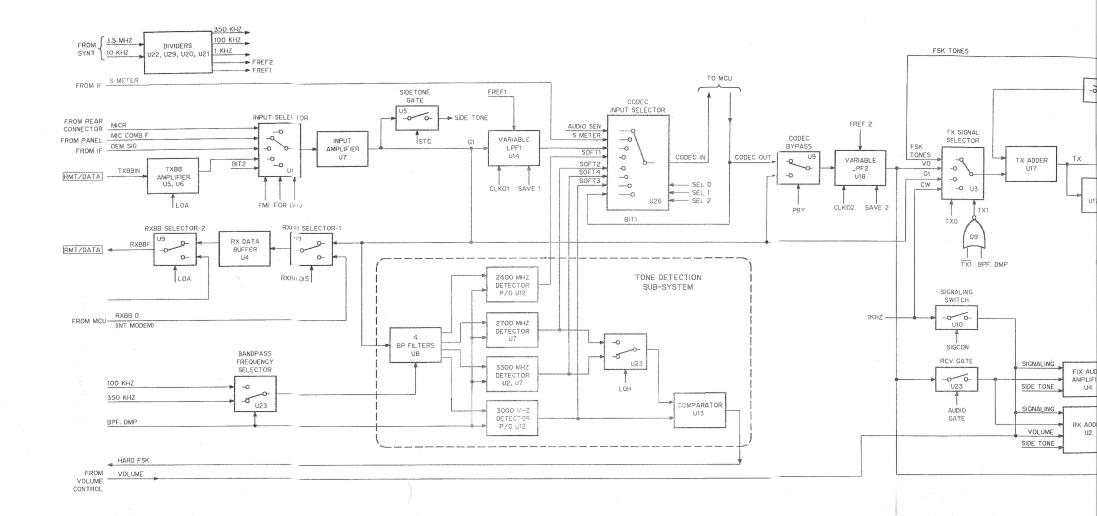

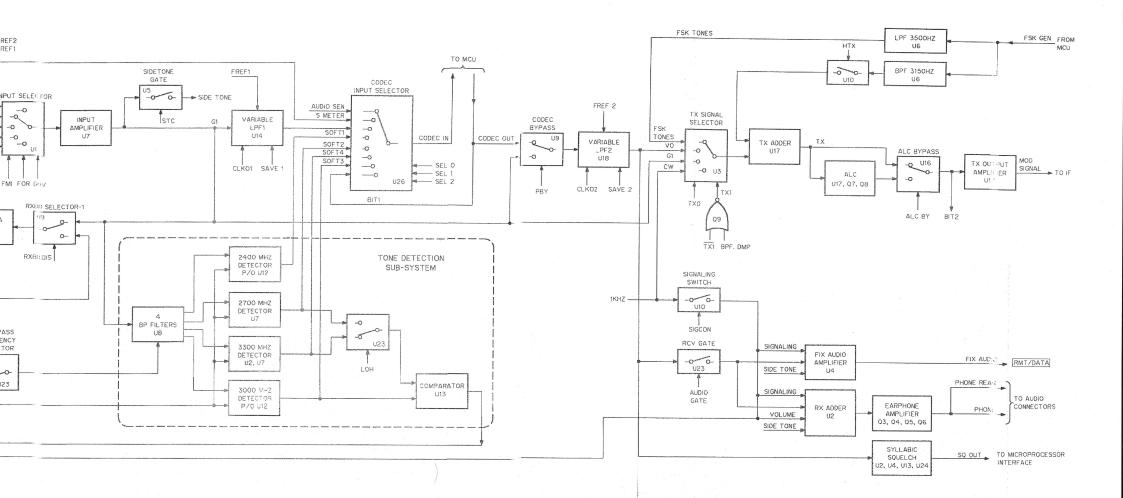

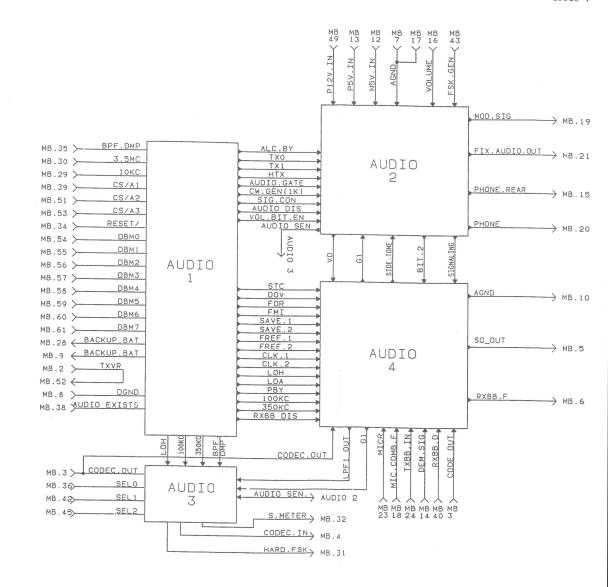

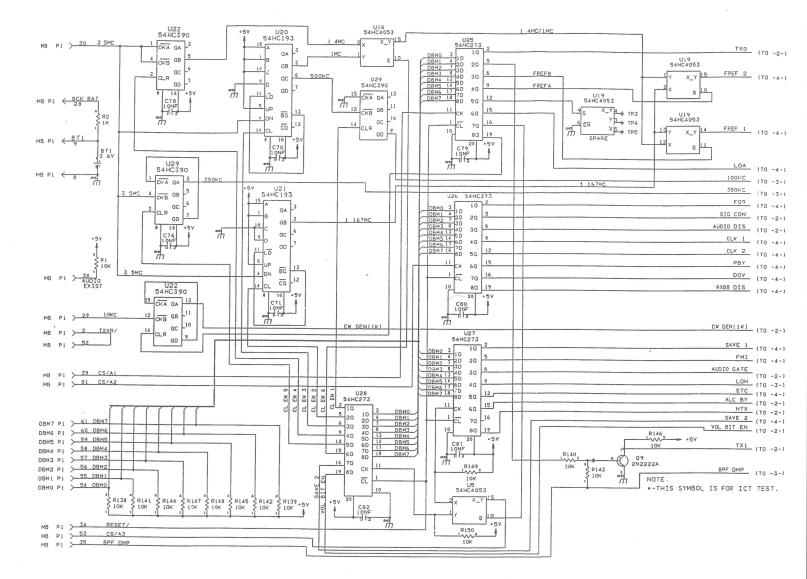

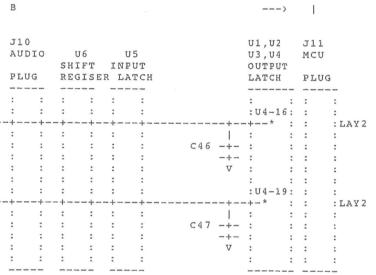

|               | 2-8                                                                                                                                                                                                                                | Module AUDIO, Signal Processing Circuits, Block Diagram      | 2-39  |

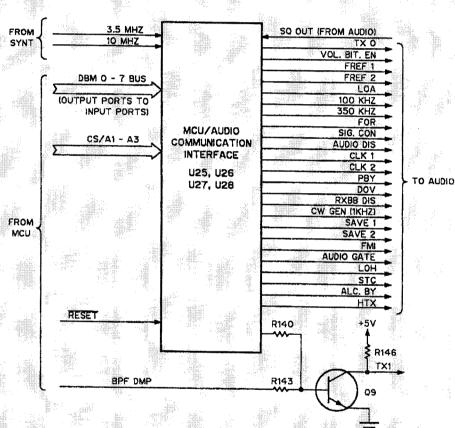

|               | 2-9                                                                                                                                                                                                                                | Module AUDIO, Interface Circuits, Block Diagram              | 2-41  |

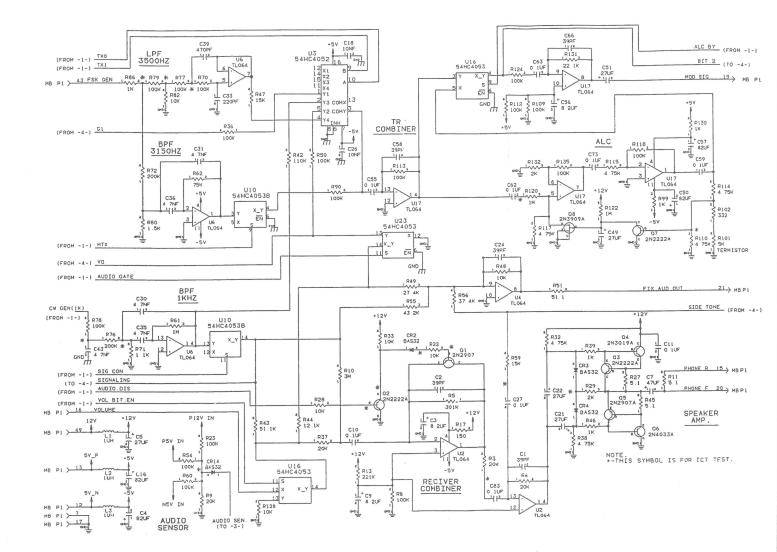

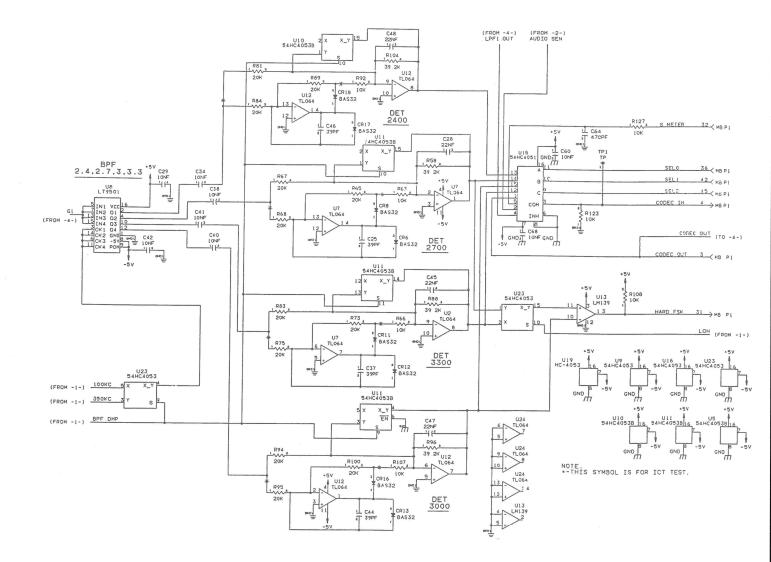

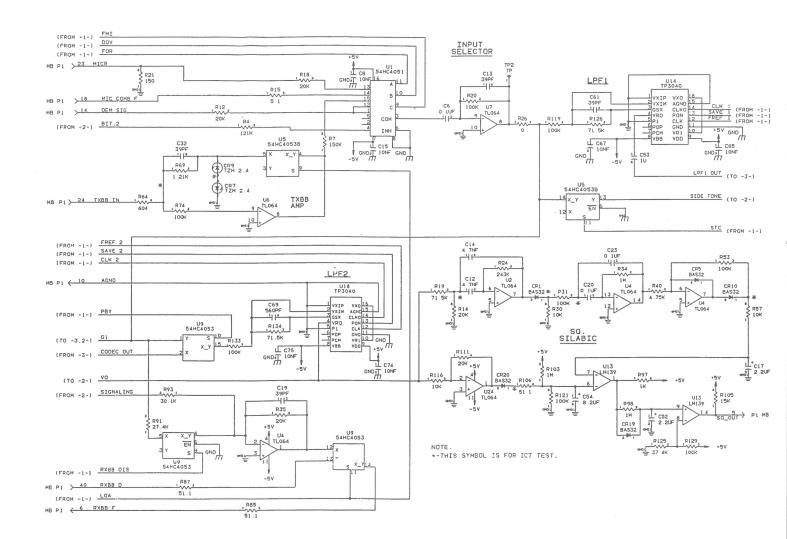

|               | 2-10.A                                                                                                                                                                                                                             | Module AUDIO, Schematic Diagram (Sheet 1 of 5)               | 2-49  |

|               | 2-10.В                                                                                                                                                                                                                             | Module AUDIO, Schematic Diagram (Sheet 2 of 5)               | 2-51  |

|               | 2-10.C                                                                                                                                                                                                                             | Module AUDIO, Schematic Diagram (Sheet 3 of 5)               | 2-53  |

|               | 2-10.D                                                                                                                                                                                                                             | Module AUDIO, Schematic Diagram (Sheet 4 of 5)               | 2-55  |

|               | 2-10.E                                                                                                                                                                                                                             | Module AUDIO, Schematic Diagram (Sheet 5 of 5)               | 2-57  |

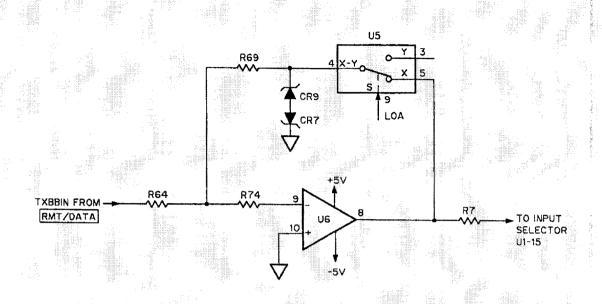

|               | 2-11                                                                                                                                                                                                                               | TX Data Buffer, Simplified Circuit                           | 2-59  |

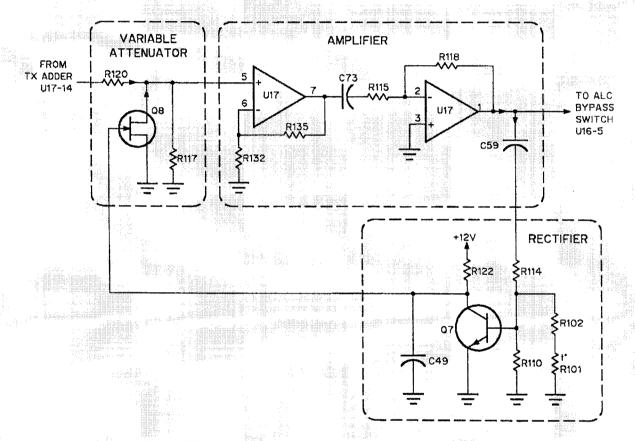

|               | 2-12                                                                                                                                                                                                                               | ALC Amplifier, Simplified Circuit                            | 2-62  |

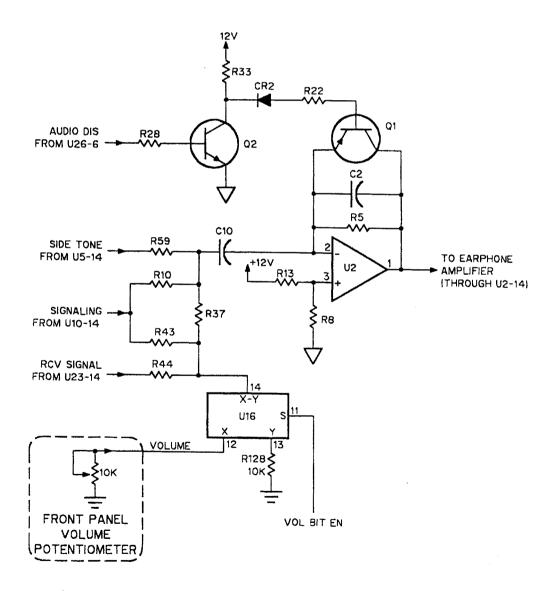

|               | 2-13                                                                                                                                                                                                                               | RX Adder, Simplified Diagram                                 | 2-67  |

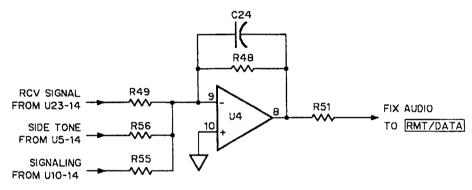

|               | 2-14                                                                                                                                                                                                                               | FIX AUDIO Amplifier, Simplified Diagram                      | 2-69  |

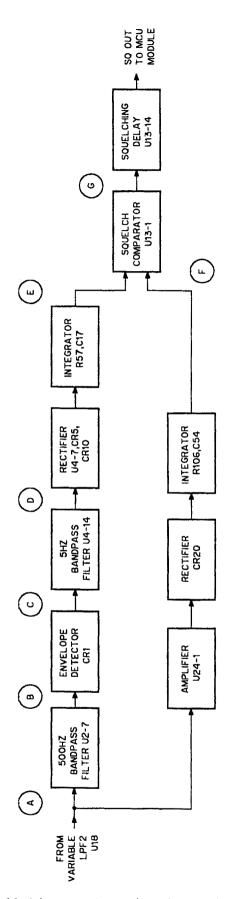

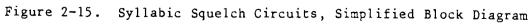

|               | 2-15                                                                                                                                                                                                                               | Syllabic Squelch Circuits, Simplified Block Diagram          | 2-71  |

|               | 2-16                                                                                                                                                                                                                               | Typical Waveforms in the Squelch Circuit                     | 2-73  |

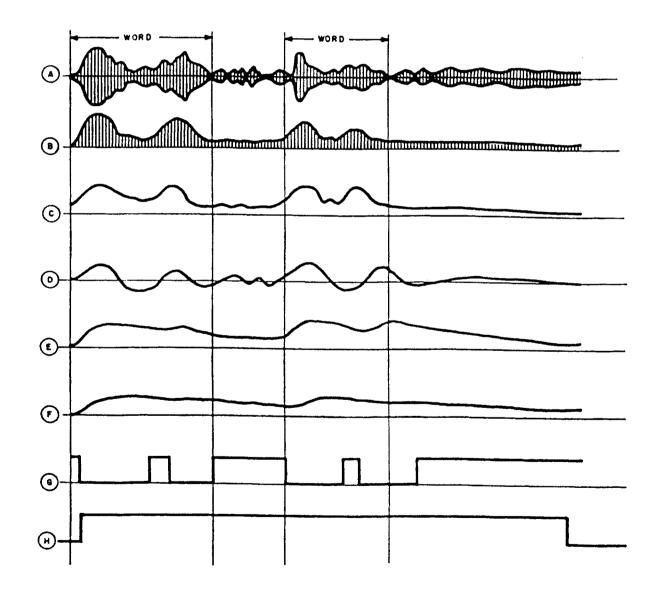

|               | 2-17                                                                                                                                                                                                                               | Module IF, Block Diagram                                     | 2-79  |

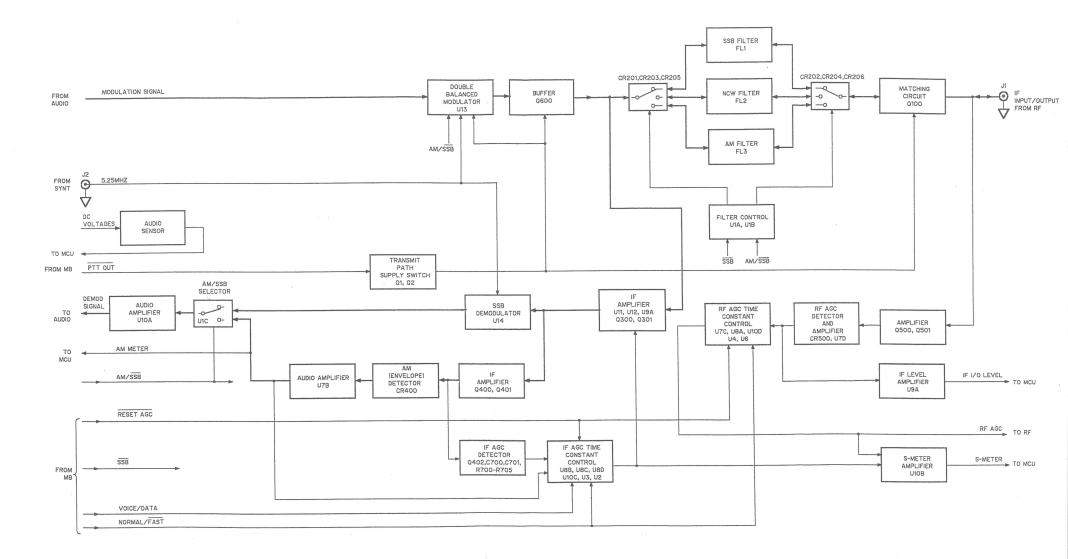

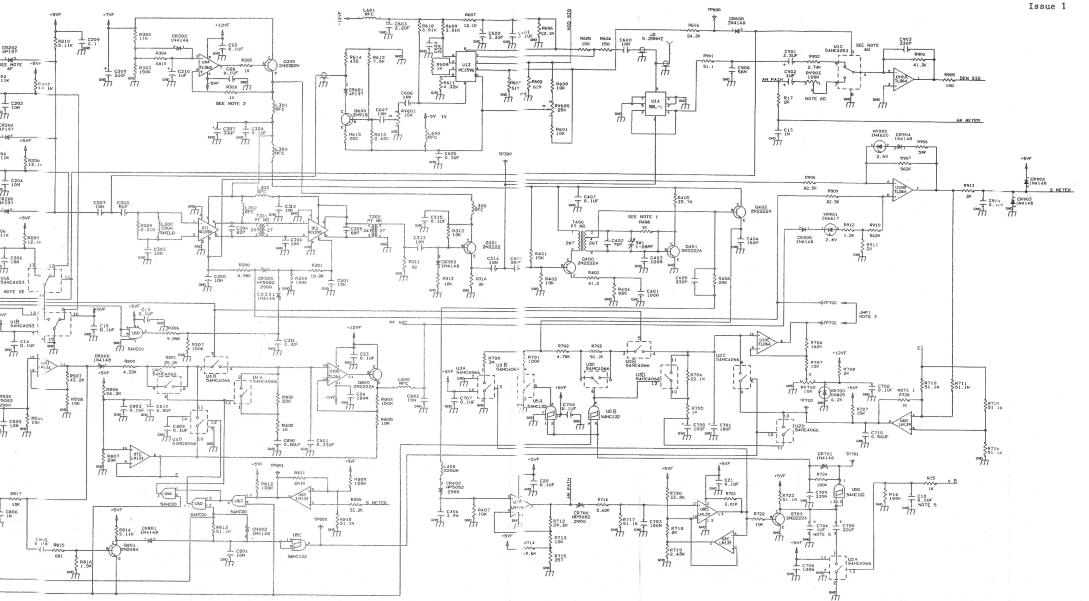

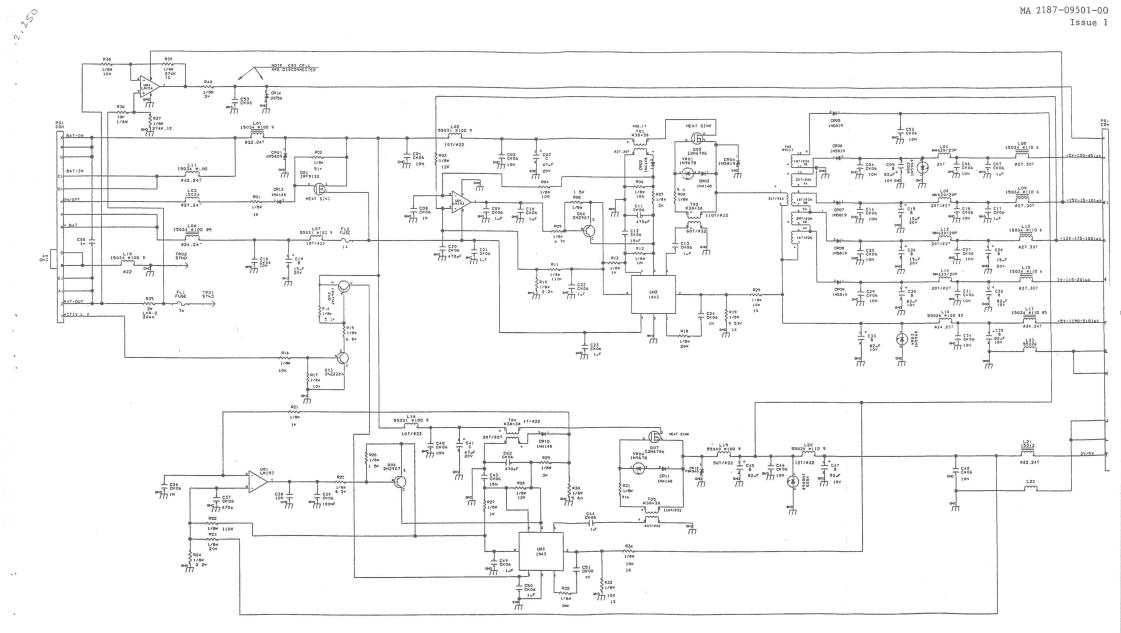

|               | 2-18                                                                                                                                                                                                                               | Module IF, Schematic Circuit Diagram                         | 2-83  |

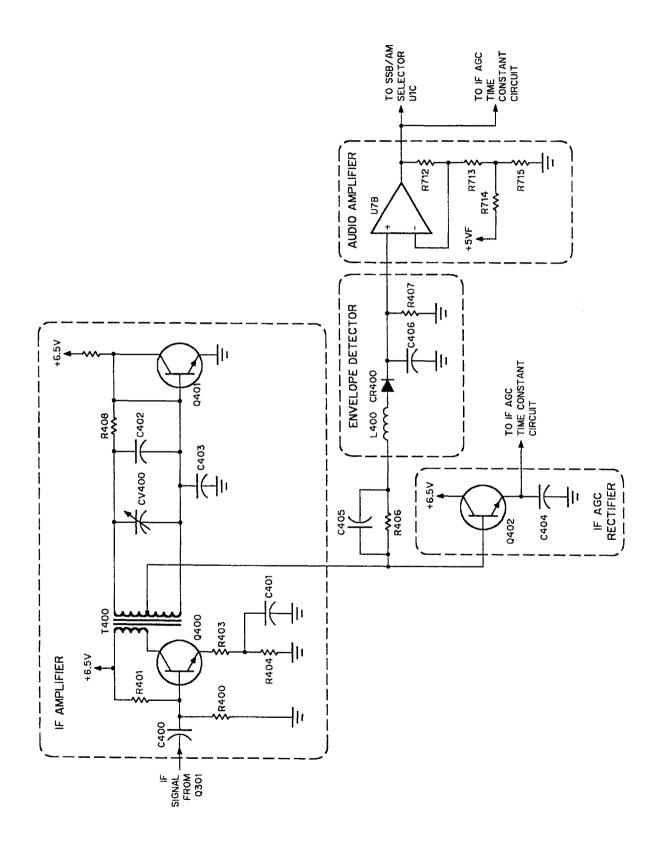

|               | 2-19                                                                                                                                                                                                                               | AM Demodulation Circuits, Simplified Diagram                 | 2-88  |

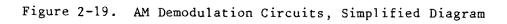

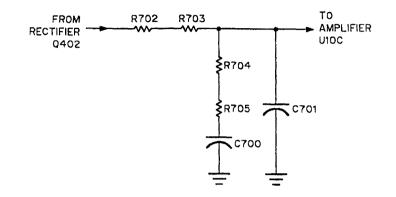

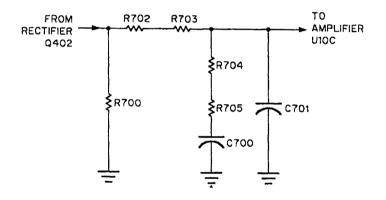

|               | 2-20                                                                                                                                                                                                                               | IF AGC Time Constant Circuits, Simplified Diagram            | 2-91  |

|               | 2-21                                                                                                                                                                                                                               | Time Constant Circuit During Attack Time, Equivalent Circuit | 2-93  |

|               | 2-22                                                                                                                                                                                                                               | Equivalent Time Constant Circuit for Slow Decrease           |       |

|               |                                                                                                                                                                                                                                    | in Received Signal                                           | 2-93  |

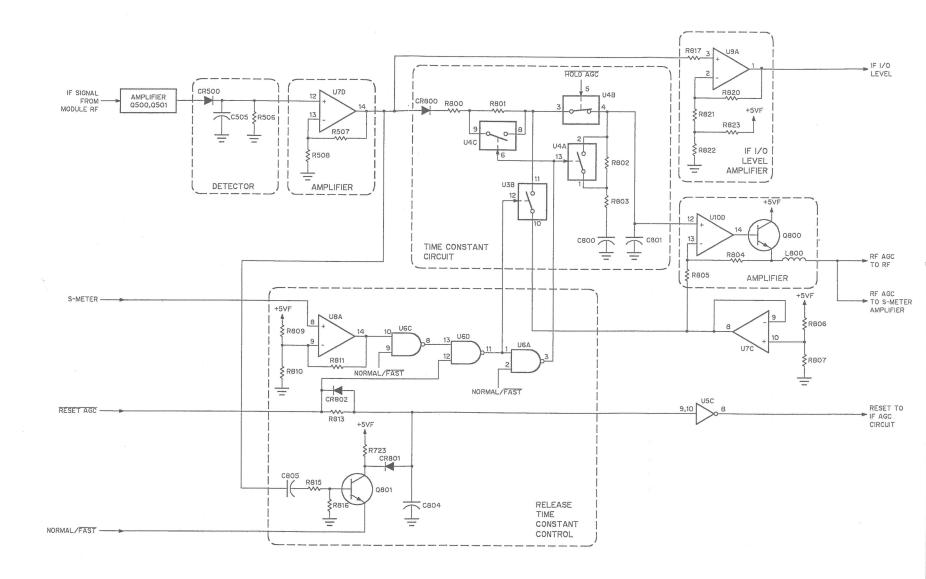

|               | 2-23                                                                                                                                                                                                                               | RF AGC, Time Constant Circuits, Simplified Diagram           | 2-97  |

|               | 2-24                                                                                                                                                                                                                               | Module RF, Block Diagram                                     | 2-103 |

|               | e e el esterez en la companya de la<br>La companya de la comp |                                                              |       |

iii

\_\_\_\_

### LIST OF ILLUSTRATIONS (Cont'd)

### Figure

#### Title

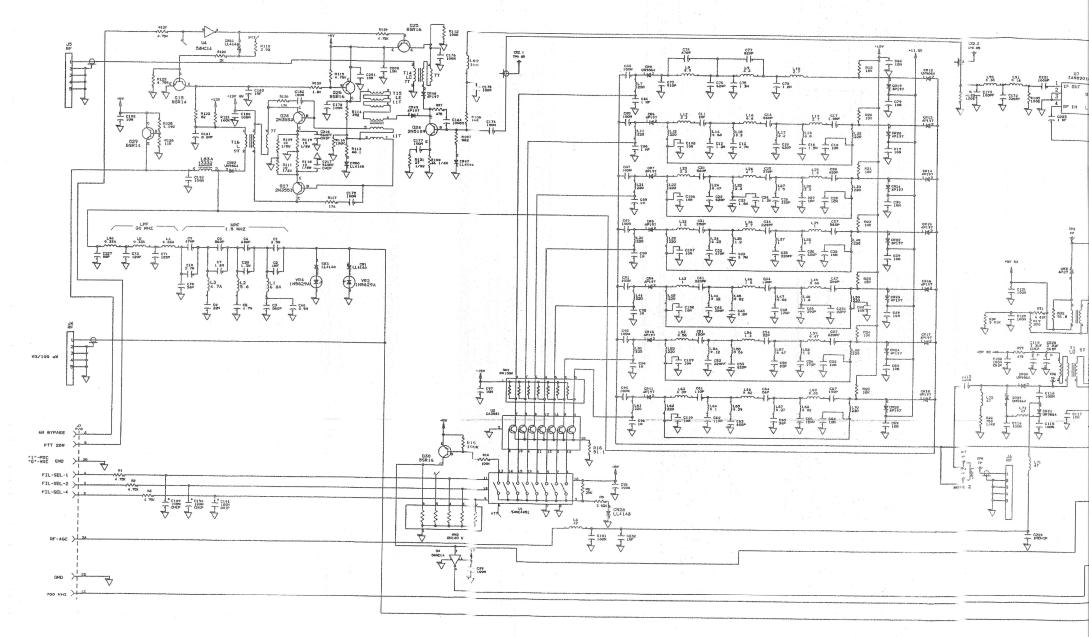

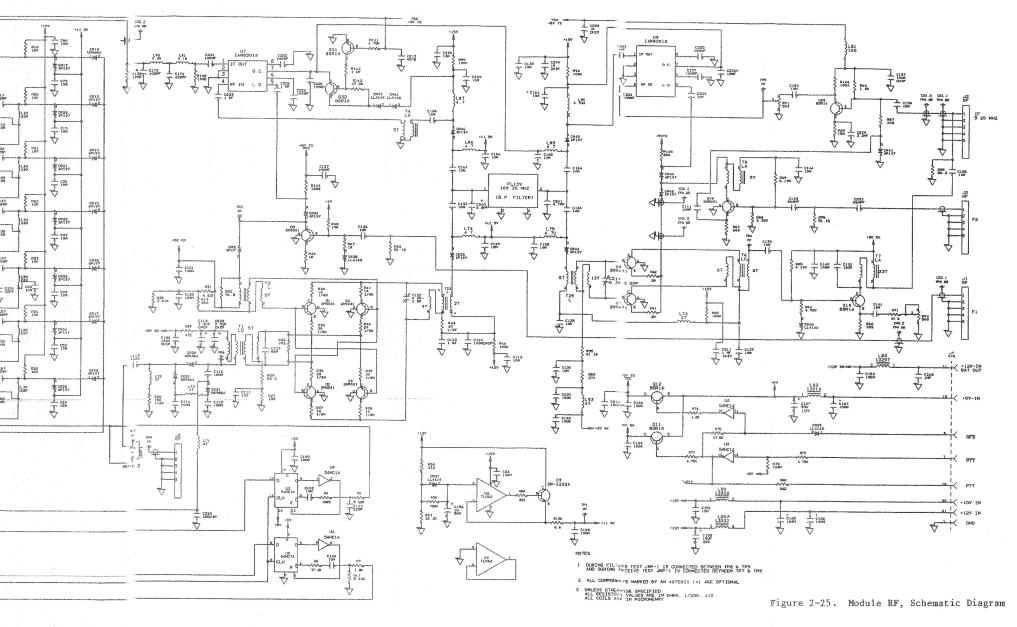

| 2-25  | Module RF, Schematic Diagram                                | 2-105 |

|-------|-------------------------------------------------------------|-------|

| 2-26  | TX/RX Control, Simplified Diagram                           | 2-109 |

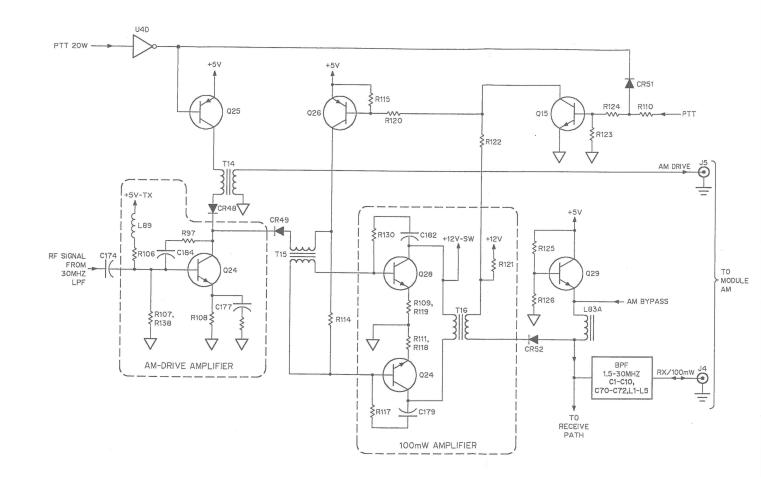

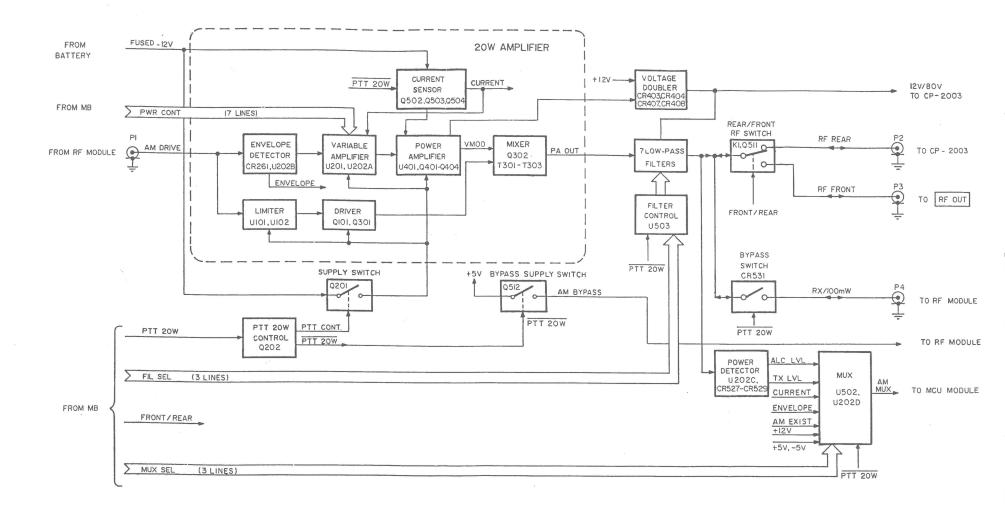

| 2-27  | Module AM, Block Diagram                                    | 2-121 |

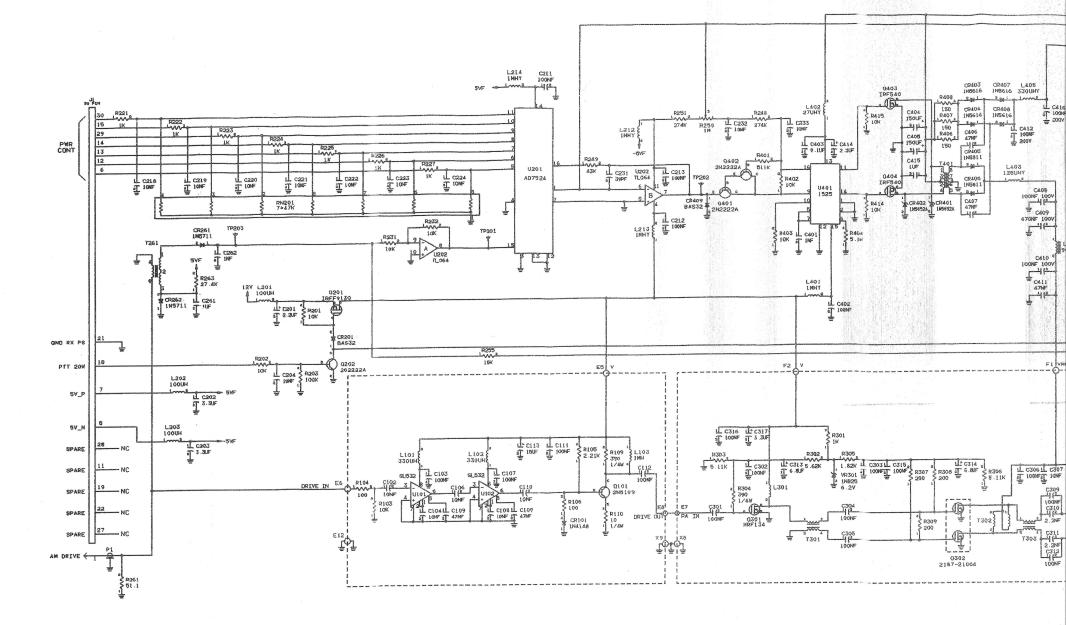

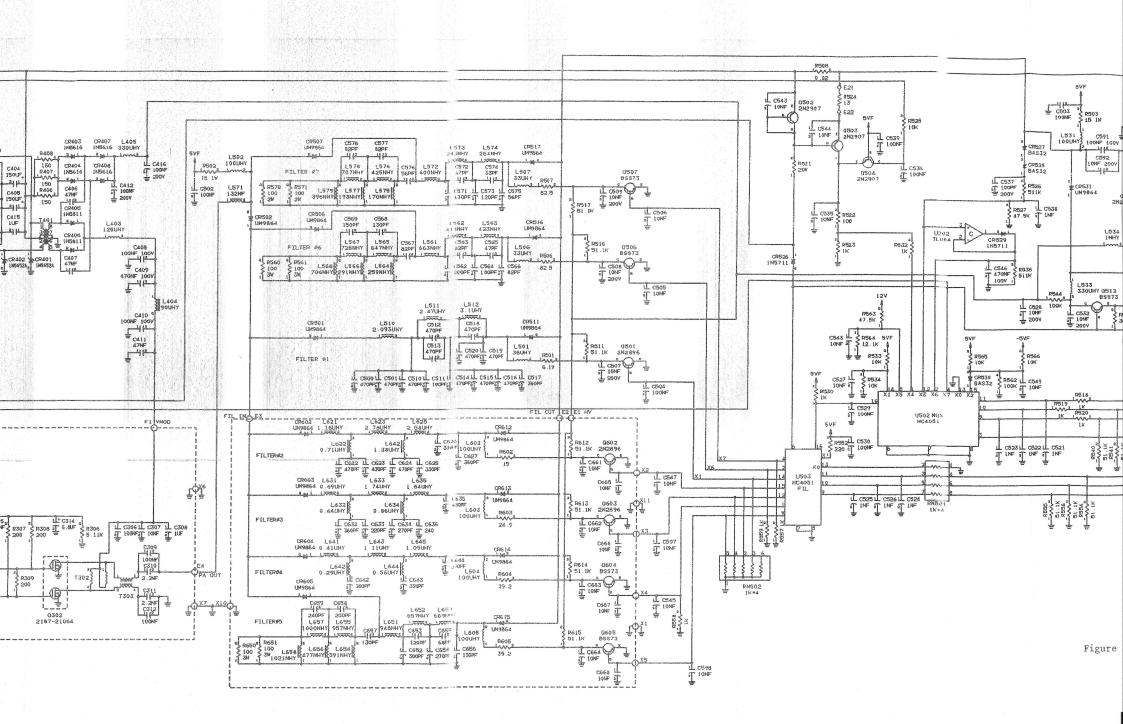

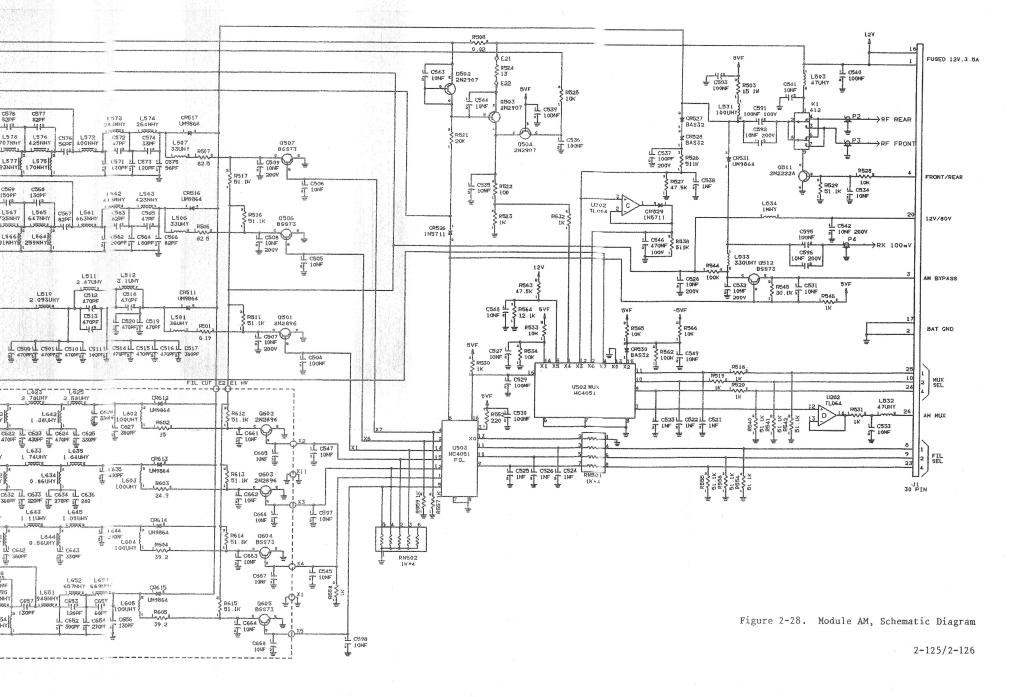

| 2-28  | Module AM, Schematic Diagram                                | 2-125 |

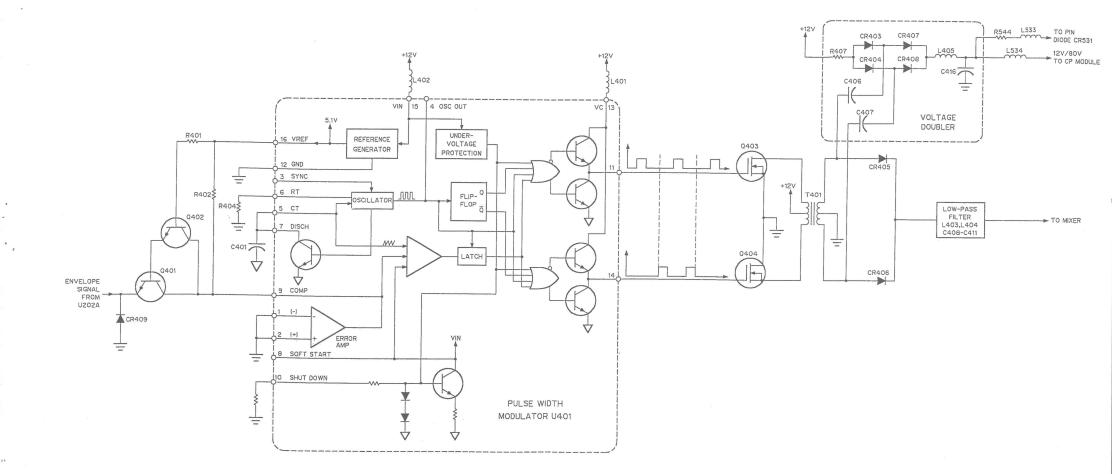

| 2-29  | Power Amplifier, Simplified Diagram                         | 2-127 |

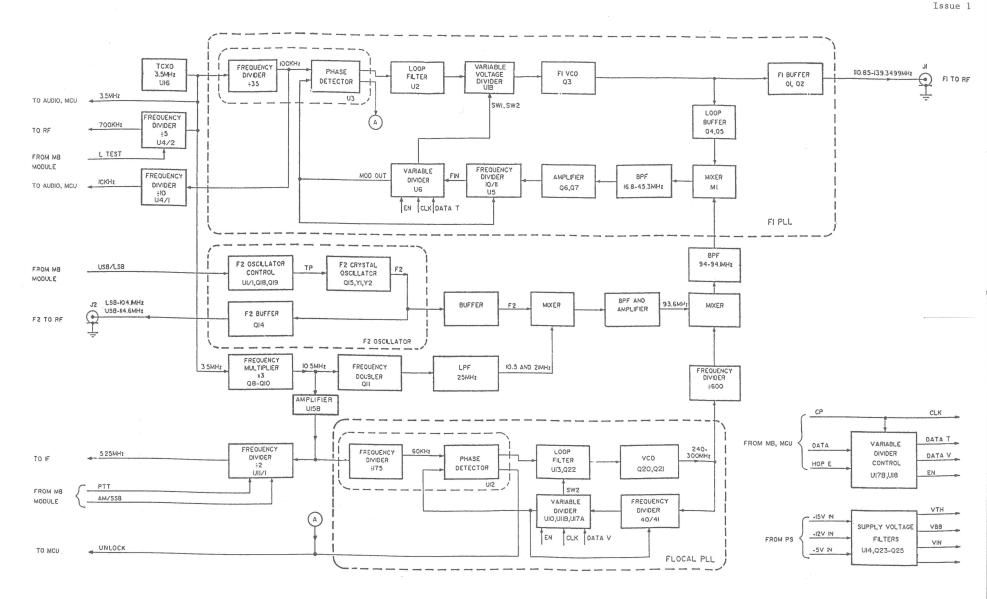

| 2-30  | Module SYNT, Block Diagram                                  | 2-137 |

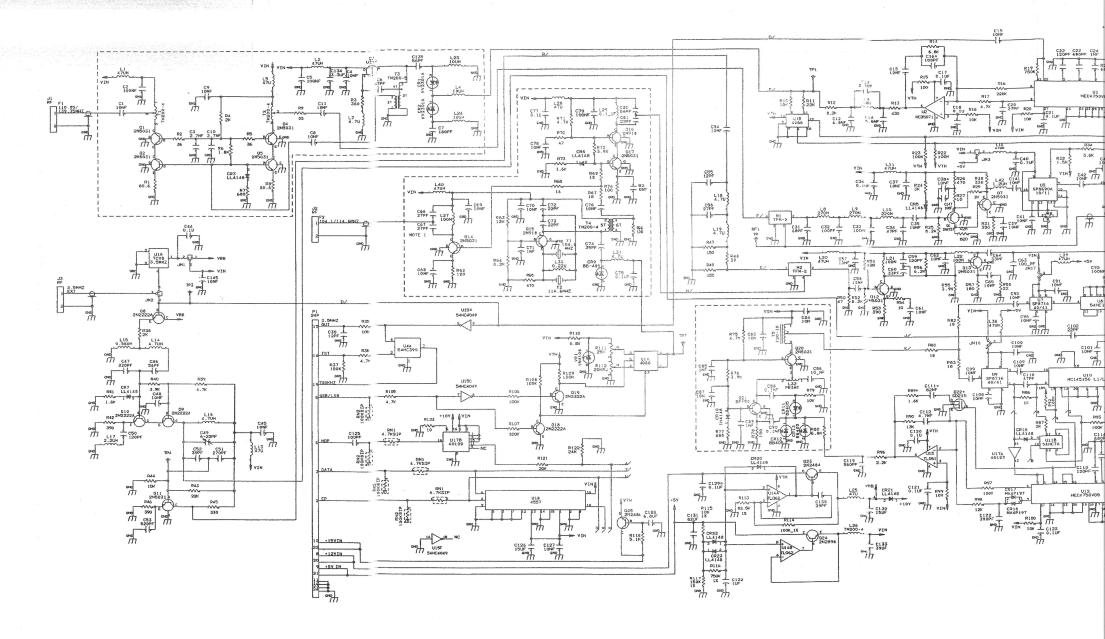

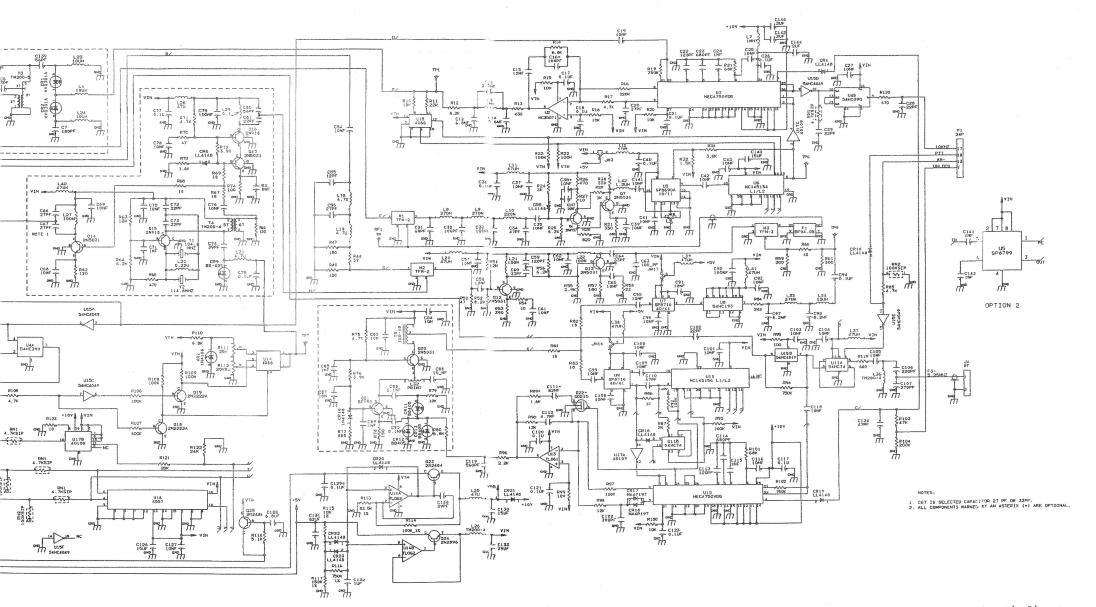

| 2-31  | Module SYNT, Schematic Diagram                              | 2-141 |

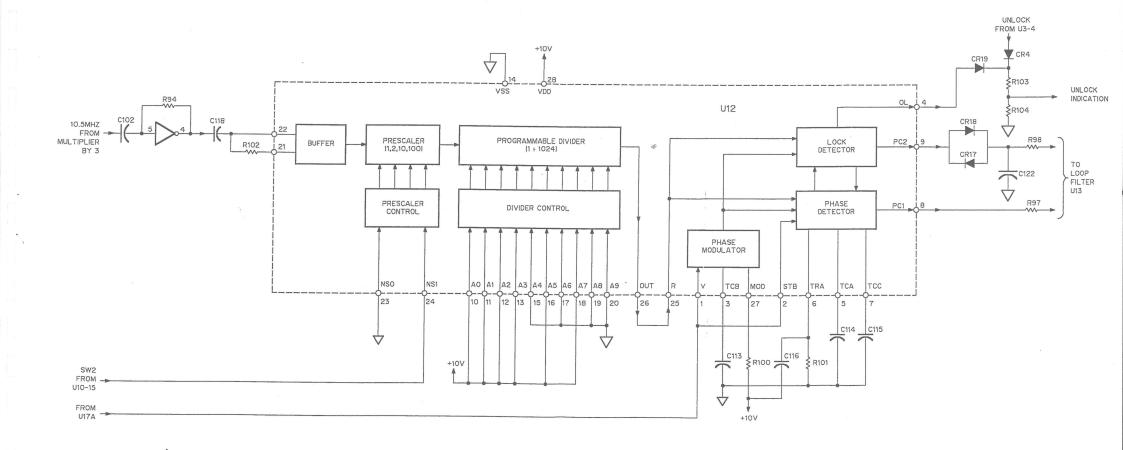

| 2-32  | Integrated Circuit Ul2, Equivalent Block Diagram            | 2-143 |

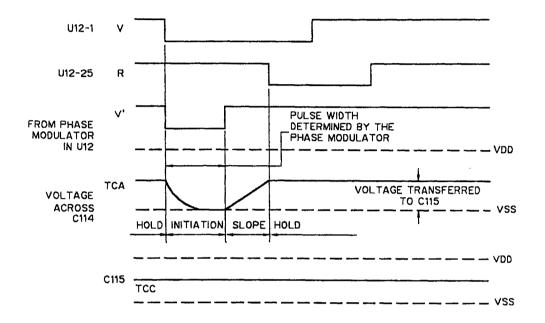

| 2-33  | Typical Phase Detector Waveforms                            | 2-147 |

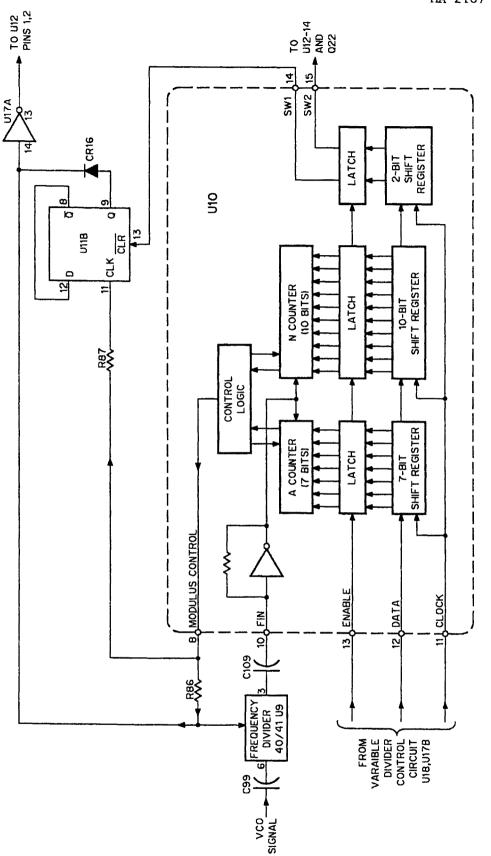

| 2-34  | Variable Divider UlO and Prescaler 40/41 Prescaler U9,      |       |

|       | Simplified Circuit Diagram                                  | 2-149 |

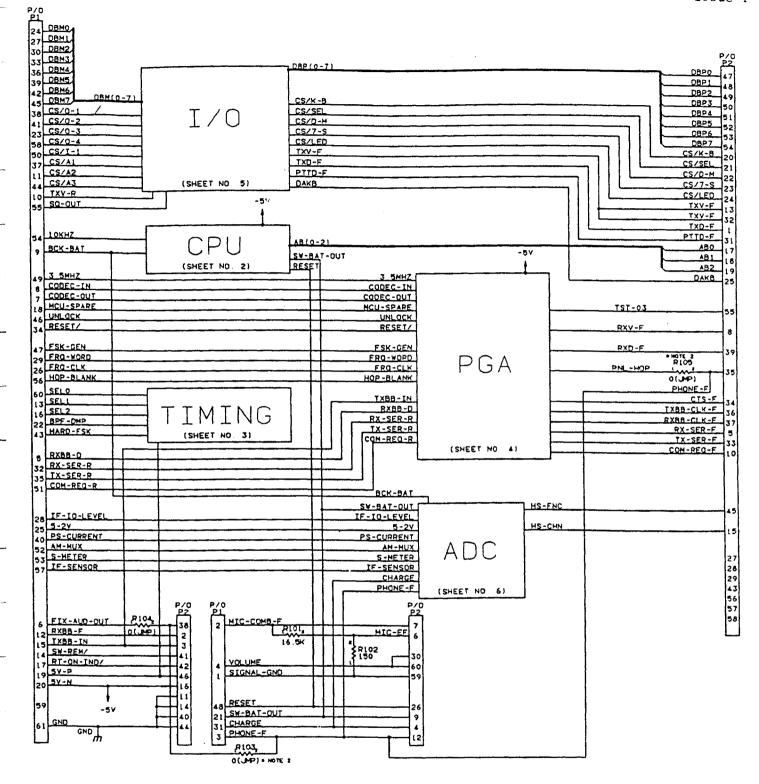

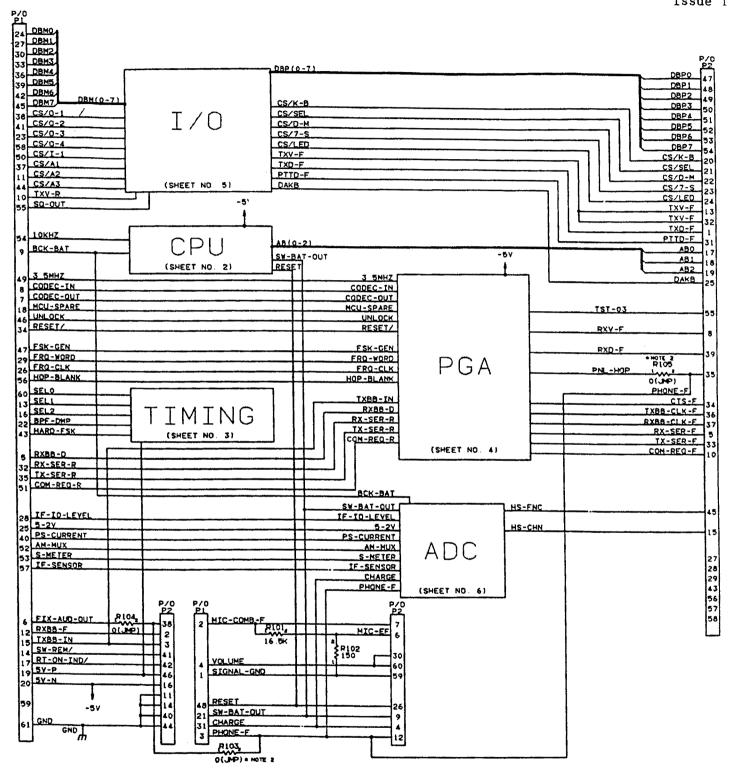

| 2-35  | Module MCU, Block Diagram                                   | 2-167 |

| 2-36  | Module MCU, Functional Interconnection and Connector        |       |

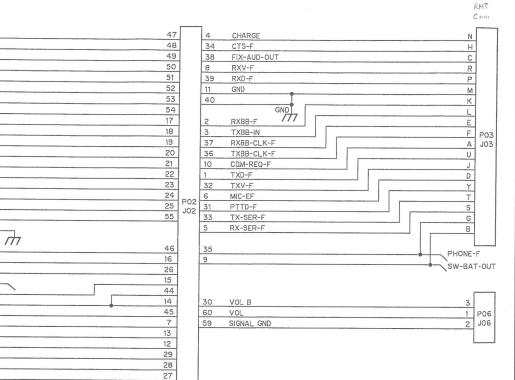

|       | Wiring Diagram                                              | 2-169 |

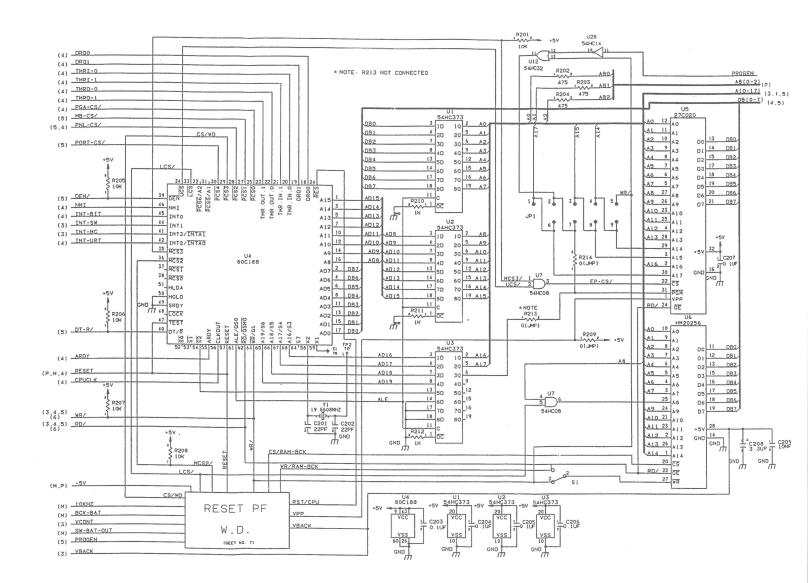

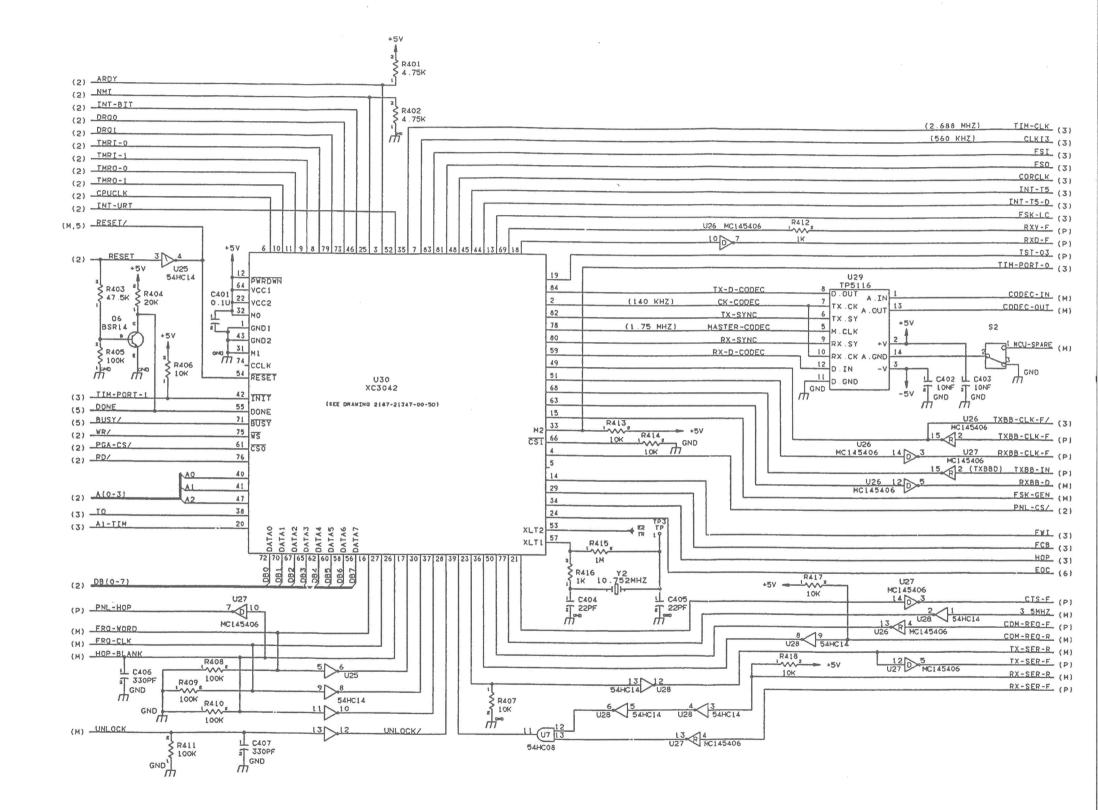

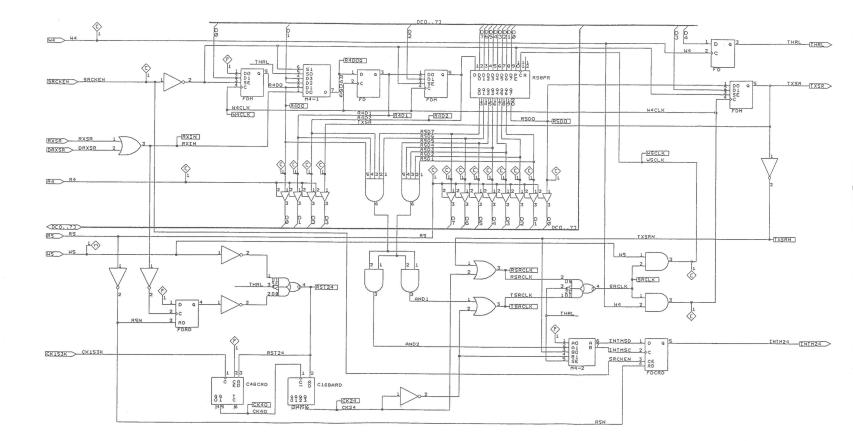

| 2-37A | Module MCU, CPU Circuit Schematic Diagram (Sheet 1 of 6)    | 2-171 |

| 2-37B | Module MCU, CPU Circuit Schematic Diagram (Sheet 2 of 6)    | 2-173 |

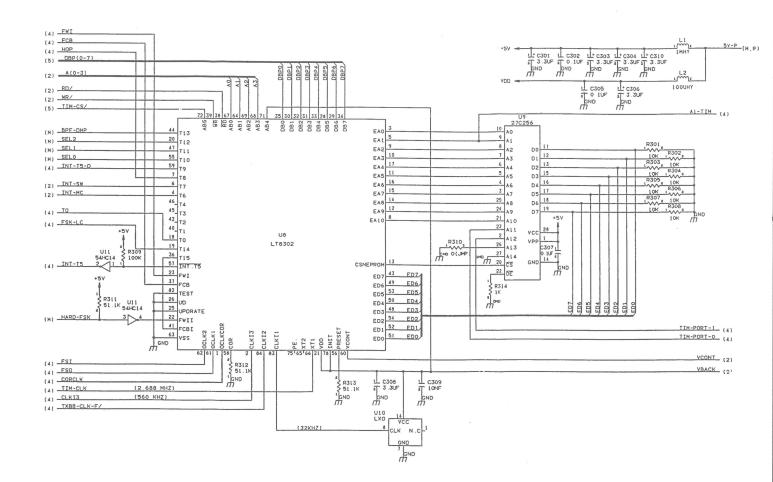

| 2-37C | Module MCU, CPU Circuit Schematic Diagram (Sheet 3 of 6)    | 2-175 |

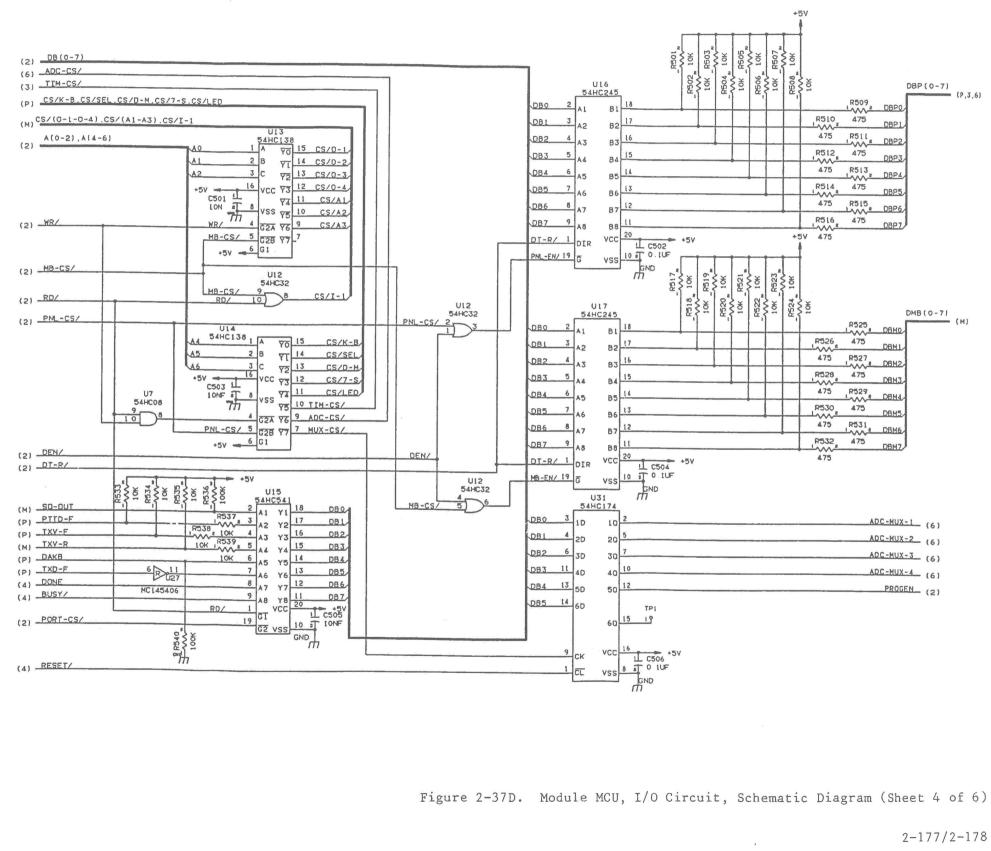

| 2-37D | Module MCU, CPU Circuit Schematic Diagram (Sheet 4 of 6)    | 2-177 |

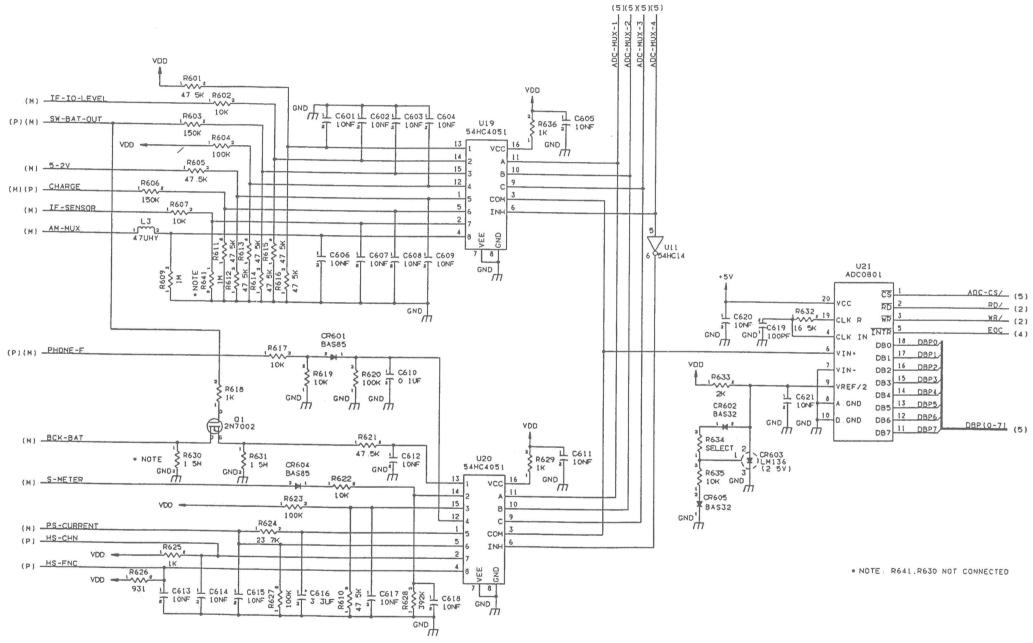

| 2-37E | Module MCU, CPU Circuit Schematic Diagram (Sheet 5 of 6)    | 2-179 |

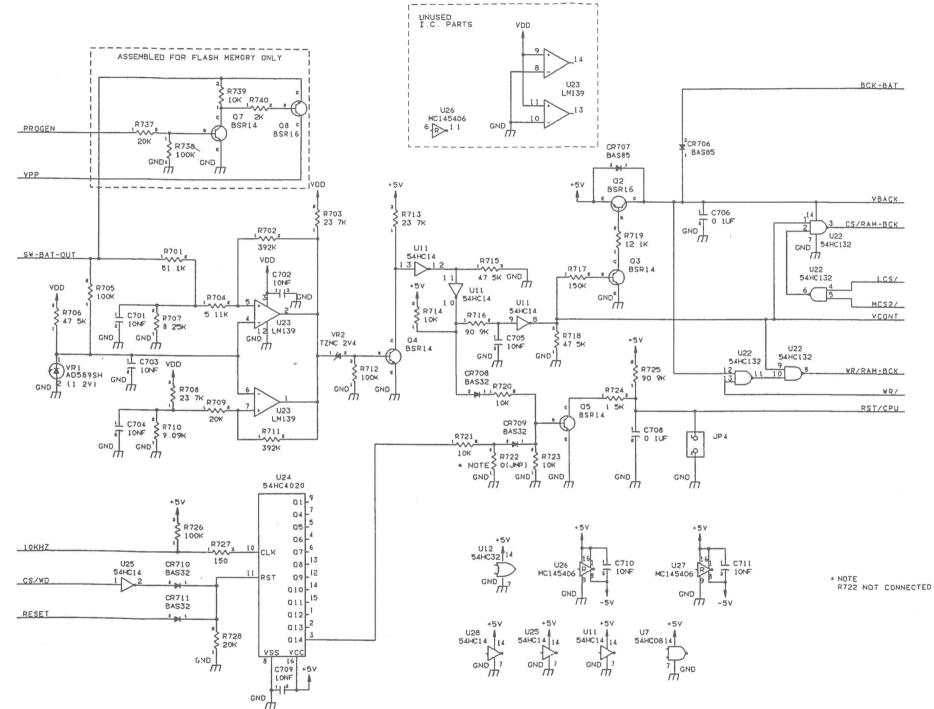

| 2-37F | Module MCU, CPU Circuit Schematic Diagram (Sheet 6 of 6)    | 2-181 |

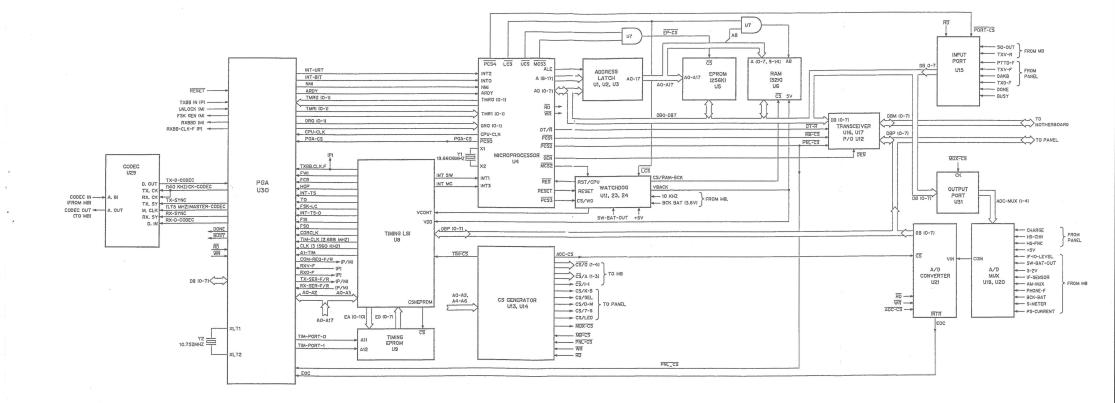

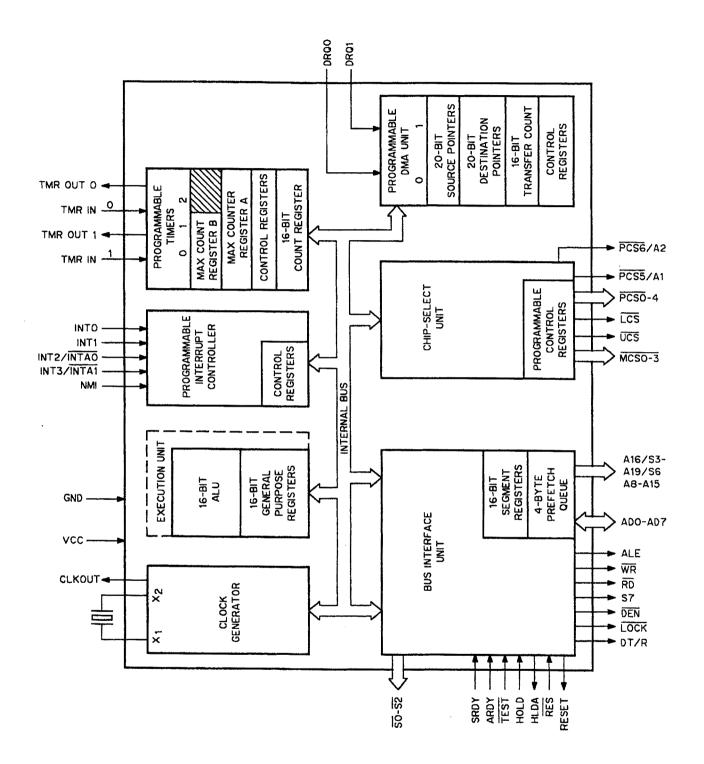

| 2-38  | Microcontroller Ul, Block Diagram                           | 2-183 |

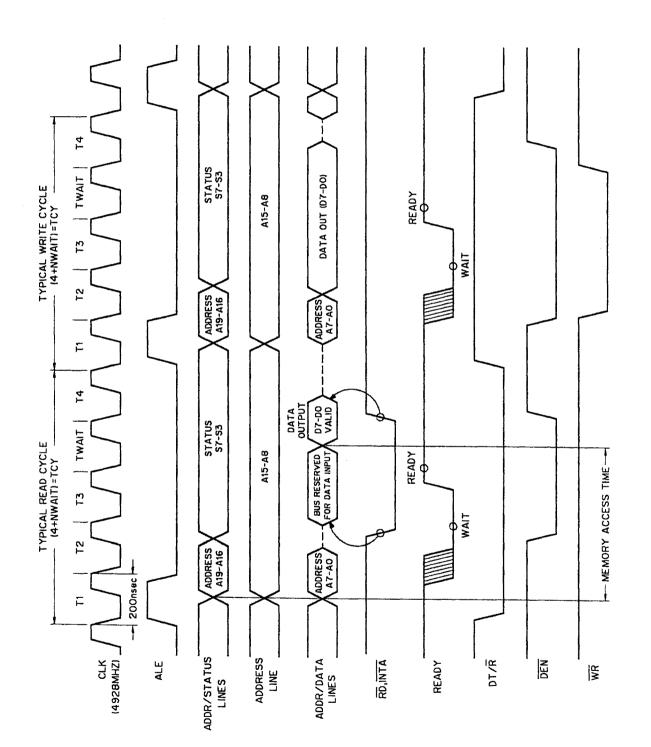

| 2-39  | Microprocessor U4, Basic System Timing                      | 2-190 |

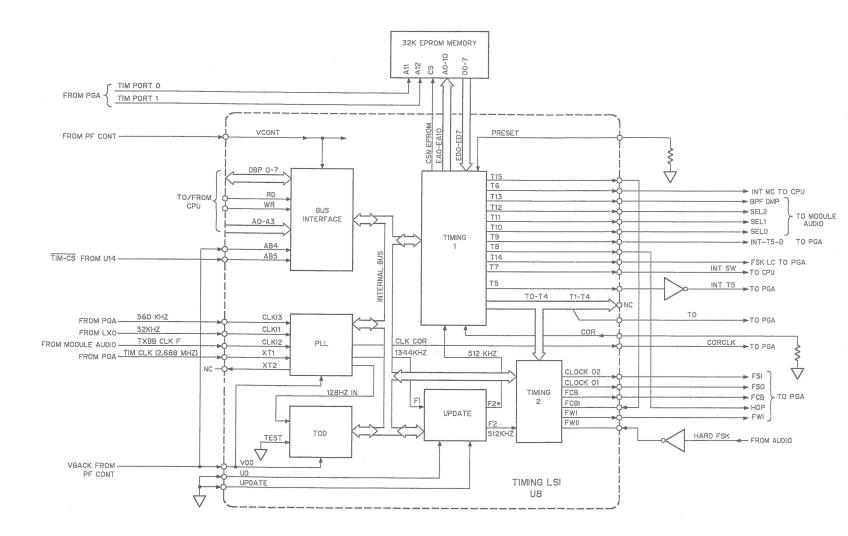

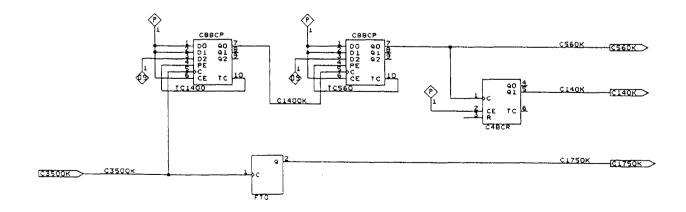

| 2-40  | TIMING LSI U8, Block Diagram                                | 2-205 |

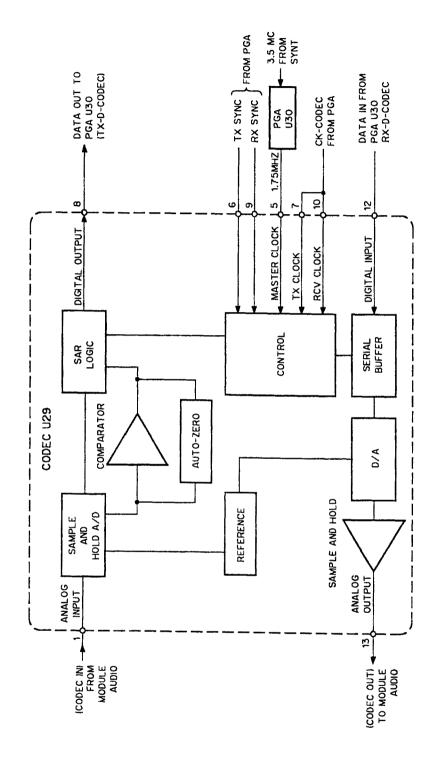

| 2-41  | Codec U29, Simplified Block Diagram                         | 2-209 |

| 2-42  | PGA, U30 - Functional Interconnection and Connector Wiring  | 2-213 |

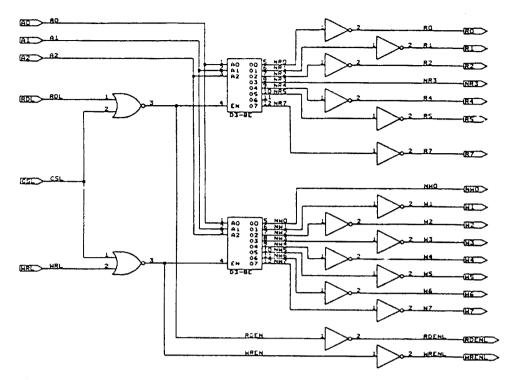

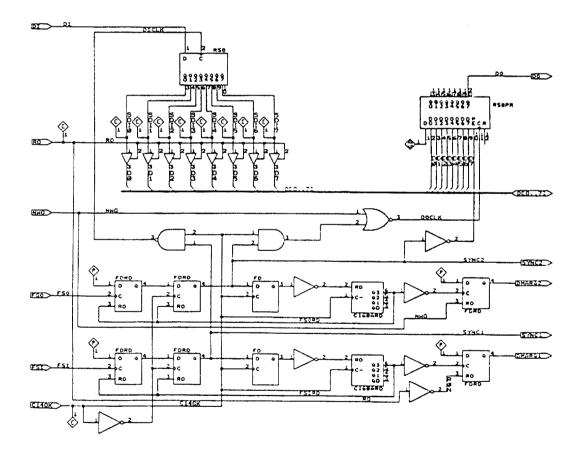

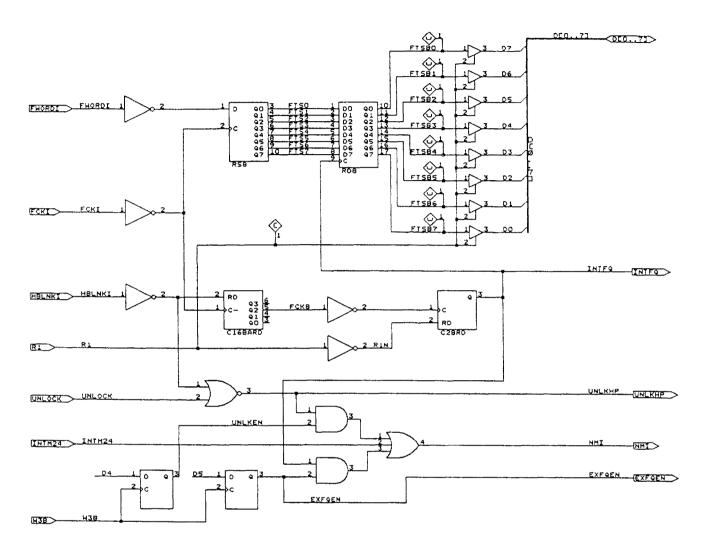

| 2-43A | PGA, U30 - PGA-S Section, Schematic Diagram (Sheet 1 of 10) | 2-215 |

| 2-43B | PGA, U30 - Codec Section, Schematic Diagram (Sheet 2 of 10) | 2-215 |

| 2-43C | PGA, U30 - FREQ TRN Section,                                |       |

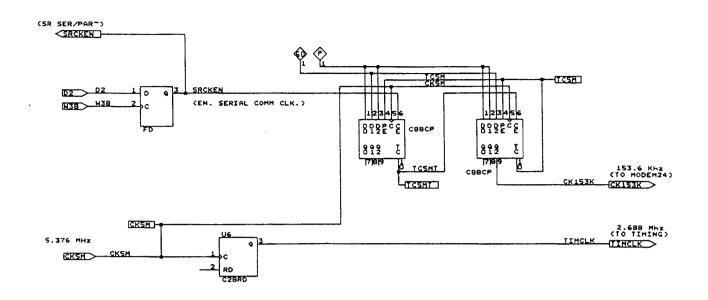

|       | Schematic Diagram (Sheet 3 of 10)                           | 2-216 |

----

:

LIST OF ILLUSTRATIONS (Cont'd)

| Figure                                                                                                          |                                                             | Page     |

|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------|

|                                                                                                                 |                                                             |          |

| 2-43D                                                                                                           | PGA, U30 - DIV3-5M Section,                                 |          |

|                                                                                                                 | Schematic Diagram (Sheet 4 of 10)                           | 2-216    |

| 2-43E                                                                                                           | PGA, U30 - DIV10M Section,                                  |          |

|                                                                                                                 | Schematic Diagram (Sheet 5 of 10)                           | 2-217    |

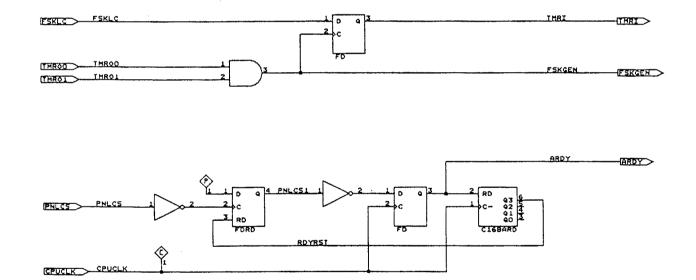

| 2-43F                                                                                                           | PGA, U30 - TIM-RDY Section,                                 |          |

| i ga ana i gi ang i ga ang i g | Schematic Diagram (Sheet 6 of 10)                           | 2-217    |

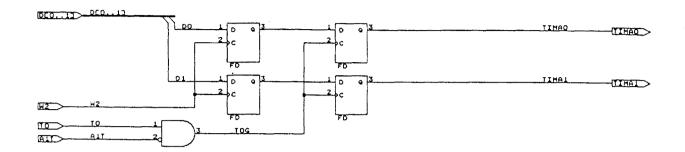

| 2-43G                                                                                                           | PGA, U30 - TIMAD Section, Schematic Diagram (Sheet 7 of 10) | 2-218    |

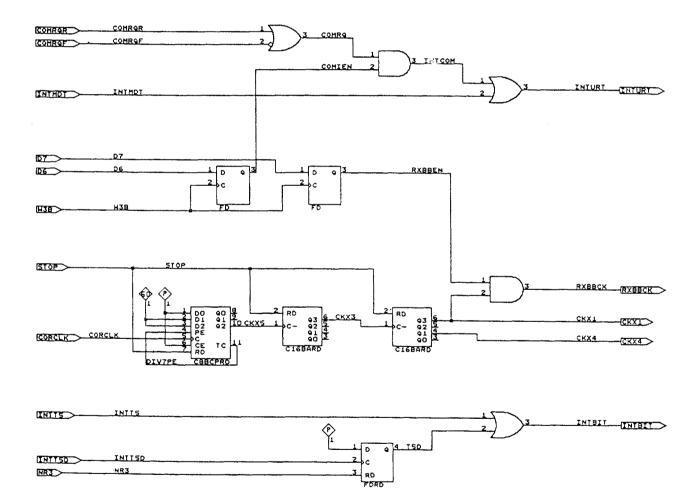

| 2-43н                                                                                                           | PGA, U30 - MISCl Section, Schematic Diagram (Sheet 8 of 10) | 2-218    |

| 2-43I                                                                                                           | PGA, U30 - MODEMDT Section,                                 |          |

|                                                                                                                 | Schematic Diagram (Sheet 9 of 10)                           | 2-219    |

| 2-43J                                                                                                           | PGA, U30 - MODEM24 Section,                                 |          |

|                                                                                                                 | Schematic Diagram (Sheet 10 of 10)                          | 2-221    |

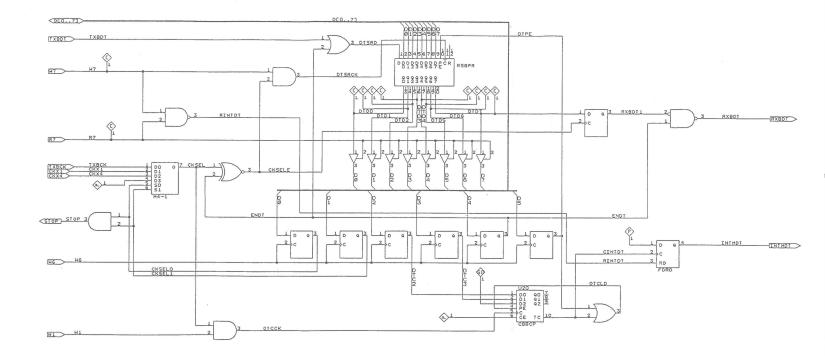

| 2-44                                                                                                            | Module PANEL, Block Diagram                                 | 2-231    |

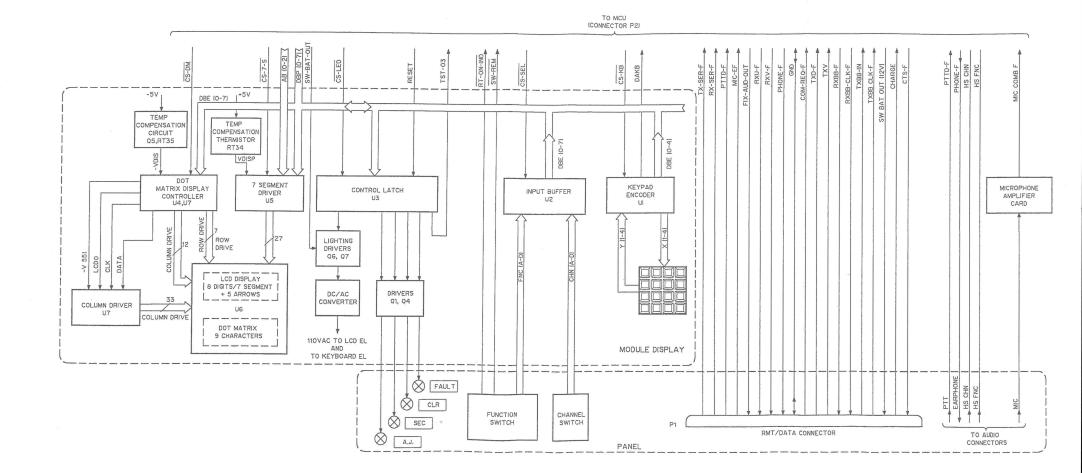

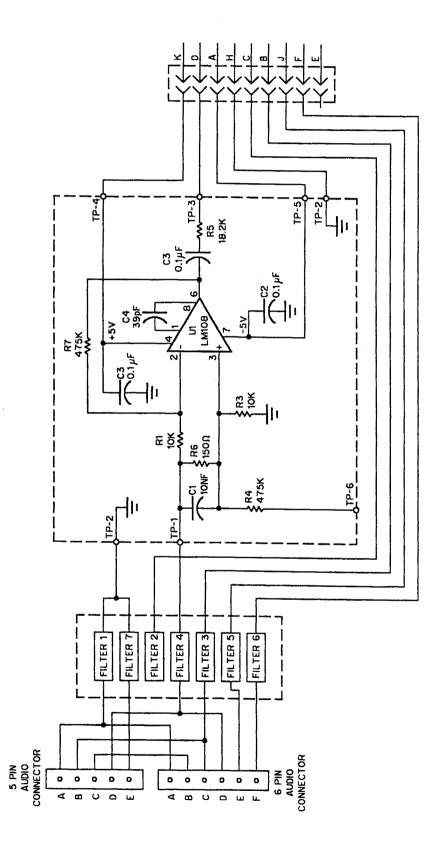

| 2-45                                                                                                            | Microphone Amplifier Card, Schematic Diagram                | 2-233    |

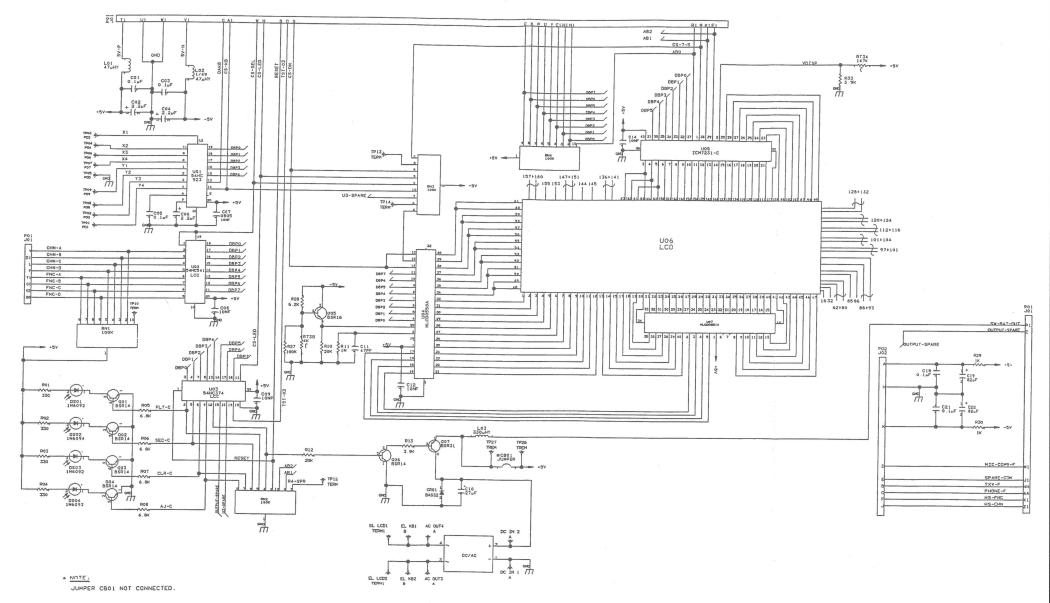

| 2-46                                                                                                            | Module DISPLAY, Schematic Diagram                           | 2-235    |

| 2-47                                                                                                            | Front Panel Flexible PCB                                    | 2-237    |

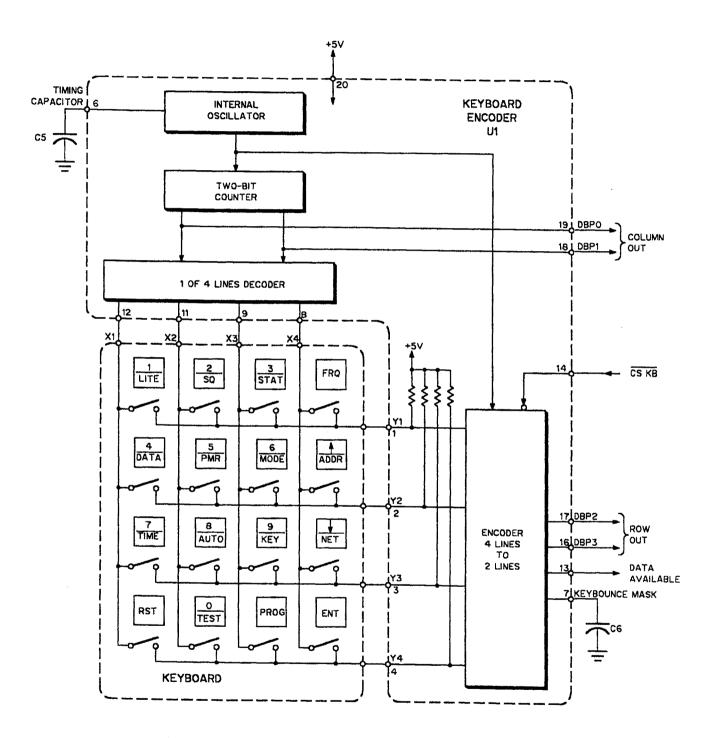

| 2-48                                                                                                            | Keypad Encoder, Simplified Diagram                          | 2-241    |

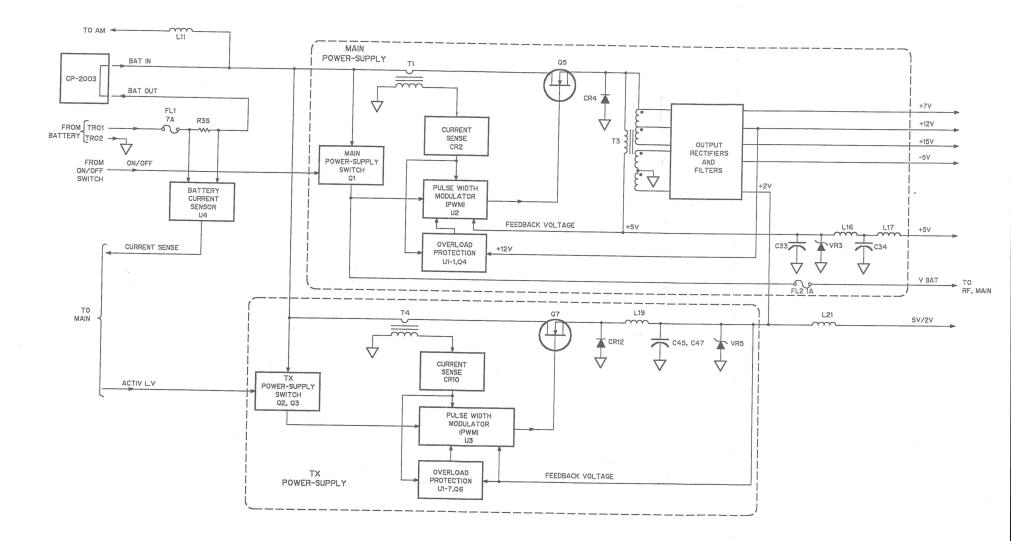

| 2-49                                                                                                            | Module PS, Block Diagram                                    | 2-247    |

| 2-50                                                                                                            | Module PS, Schematic Diagram                                | 2-251    |

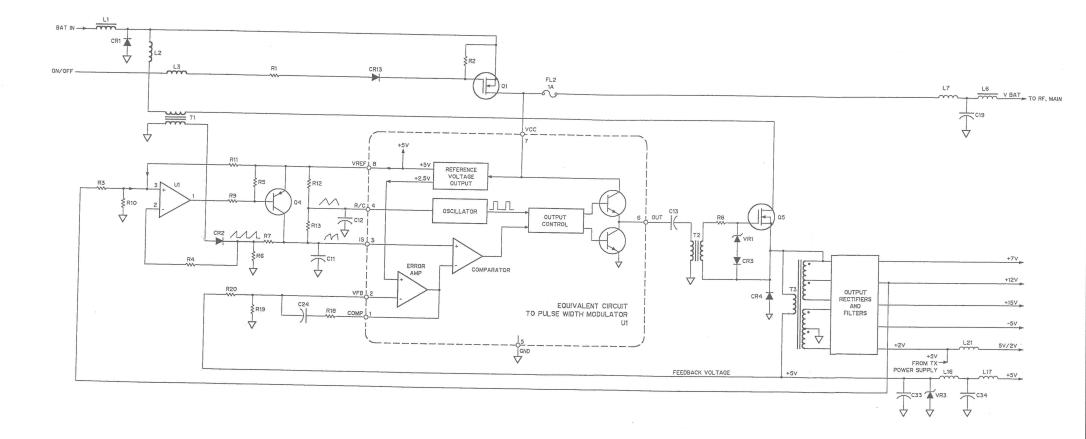

| 2-51                                                                                                            | Main Power Supply, Simplified Diagram                       | 2-253    |

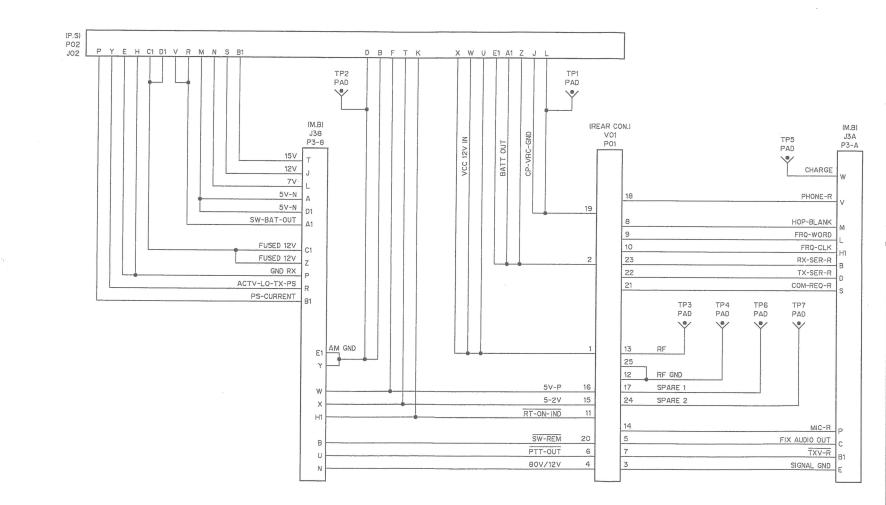

| 2-52                                                                                                            | Module MB, Block Diagram                                    | 2-258    |

| 2-53                                                                                                            | Module MB, Schematic Diagram                                | 2-259    |

| 2-54                                                                                                            | Rear Flexible Printed Board, Wiring Diagram                 | 2-261    |

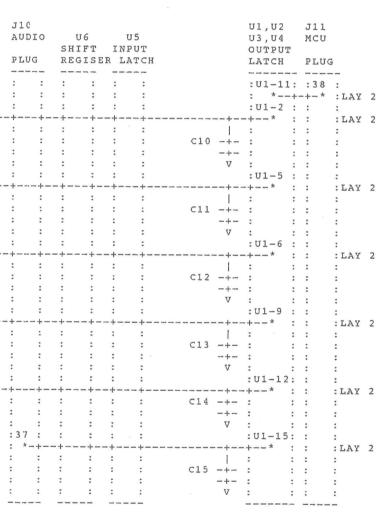

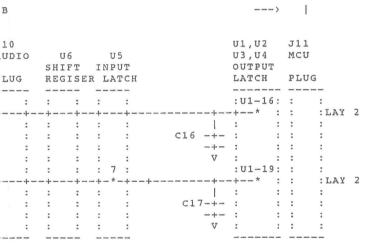

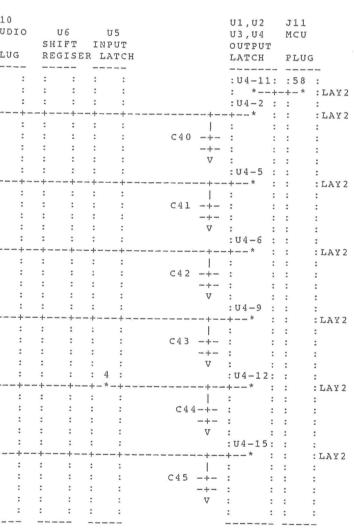

| 2-55.A                                                                                                          | Audio Signals and Control Lines (sheet 1 of 2)              | 2-267    |

| 2-55.A                                                                                                          | Audio Signals and Control Lines (sheet 2 of 2)              | 2-269    |

| 2-55.B                                                                                                          | Clock Signals and Indication Lines                          | 2-271    |

| 2-55.C                                                                                                          | Voltage Lines (sheet 1 of 3)                                | 2-273    |

| 2-55.C                                                                                                          | Voltage Lines (sheet 2 of 3)                                | 2-275    |

| 2-55.C                                                                                                          | Voltage Lines (sheet 3 of 3)                                | 2-277    |

|                                                                                                                 |                                                             |          |

|                                                                                                                 |                                                             |          |

|                                                                                                                 |                                                             |          |

|                                                                                                                 |                                                             | <b>v</b> |

|                                                                                                                 |                                                             |          |

|                                                                                                                 |                                                             |          |

#### LIST OF ILLUSTRATIONS (Cont'd)

#### Figure

Title Page 2-55.D Communication Lines 2-279 2-55.E Input Signals 2-281 2-55.F General Control Lines (sheet 1 of 2) 2-283 2-55.F General Control Lines (sheet 2 of 2) 2-285 2-55.G Power Control Lines 2-287 2-55.H AGC Control Lines 2-289 2-55.I TX/RX Control Lines 2-291 General Control Lines (sheet 1 of 2) 2-55.J 2-293 General Control Lines (sheet 2 of 2) 2-55.J 2-295 2-55.K Spare Lines (sheet 1 of 3) 2-297 2-55.K Spare Lines (sheet 2 of 3) 2-299 2-55.K Spare Lines (sheet 3 of 3) 2-301 2-55.L Coaxial Lines 2-303 2-56 Antenna Coupler RF Section, Block Diagram 2-307 2-57 Module RF3, Schematic Diagram 2-309 2-58 TUNE/NORM Switch, Simplified Diagram 2 - 3112-59 Sensor Assembly, Block Diagram 2-317 2-60 Sensor Assembly, Schematic Diagram 2-319 2-61 PH-H Phase Sensor, Simplified Diagram and Typical Phasor Diagram 2-321 2-62 Forward Power Detector Operation 2-323 2-63 G Sensor Operation 2-326 2-64 R and VSWR Sensors, Simplified Diagram 2-330 2-65 Resistance Sensor Operation 2-331 2-66 Reflected Power Detector, Typical Phasor Diagrams 2-333 2-67 Module RF2, Schematic Diagram 2-335 2-68 Module RF1, Schematic Diagram 2-339

2 - 343

Module MNC, Block Diagram

2-69

# LIST OF ILLUSTRATIONS (Cont'd)

MA 2187-09501-00 Issue 1

vii

#### Title

| Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Title                                                    | Page  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------|

| 2-70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Module MNC, Microcontroller Block Diagram                | 2-347 |

| 2-71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Module MNC, Functional Interconnection Diagram           | 2-353 |

| 2-72A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Module MNC, Schematic Diagram (Sheet 1 of 2)             | 2-355 |

| 2-72B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Module MNC, Schematic Diagram (Sheet 2 of 2)             | 2-357 |

| 2-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PTT Transition Detector Operation                        | 2-362 |

| 2-74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MNC Module, Software Organization                        | 2-366 |

| 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Test Set-up No.1                                         | 3-14  |

| 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Test Set-up No.2                                         | 3-14  |

| 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Test Set-up No.3                                         | 3-14  |

| 3-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Test Set-up No.4                                         | 3-15  |

| 3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Test Set-up No.5                                         | 3-15  |

| 3-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Cover Identification                                     | 3-72  |

| 3-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Gasket Installation                                      | 3-73  |

| 3-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RT-2001, Front Panel Components                          | 3-76  |

| 3-9.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | View on Modules Side (Sheet 1 of 2)                      | 3-80  |

| 3-9.В                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | View on Modules Side (Sheet 2 of 2)                      | 3-81  |

| 3-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | View on Motherboard Side                                 | 3-82  |

| 3-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Module PS, Solder Side                                   | 3-87  |

| 3-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Module PS, Fuse Location                                 | 3-88  |

| 3-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CP-2003, External View                                   | 3-89  |

| 3-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Modules RF1/RF2 and RF3 Assembly                         | 3-90  |

| 3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | WHIP/DIP Switch and Wiring                               | 3-92  |

| 3-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Module AUDIO, Component Side with Battery Card Installed | 3-95  |

| 3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Module AUDIO, Solder Side                                | 3-95  |

| 3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Module AUDIO, Component Side, Battery Card Removed       | 3-95  |

| <ul> <li>A provide the contract of the con</li></ul> |                                                          |       |

Figure

Table

viii